**Rita Lovassy**

# **Digital Technics**

Kandó Kálmán Faculty of Electrical Engineering Óbuda University Budapest, 2013

# Preface

Digital circuits address the growing need for computer networking communications in the technological world today. Starting from the development of the integrated circuit in 1959 there has been a continuous interest in the understanding of new digital devices capable of performing complex functions.

It is the intent of this book to give an overview of the basic concepts and applications of digital technics, from Boolean algebra to microprocessors. The book highlights the distinction between combinational circuits and sequential circuits, deals with numeral systems, and gives a clear overview of main digital circuits, starting from gates through latches and flip-flops.

In the case of combinational circuits, further distinction between logic circuits and arithmetic circuits is provided. Furthermore, in the last two chapters, the book develops, in detail, the main memory structures, gives a basic microcomputer organization, and introduces a typical 8-bit microprocessor.

The material in this book is suitable for one or two semesters' course of the bachelors' degree program in electrical engineering or is also well-fitted for self study. The aim is to acquaint the future engineers with the fundamentals of digital technics, digital circuits, and with their characteristics and applications.

The book includes, as additional features, comprehensive examples and figures. At the end of each chapter a series of problems are given, which intend to give a broader view of the applicability of the concepts.

This book could be readily used in a completely new approach, as follows:

- 1. Number systems (Chapter 2)

- 2. Combinational logic networks (subsection 1.5) with various Boolean logic gates followed by switches and implementation of Boolean logic gates using transistors (subsection 3.1. Then the topics related to Boolean algebra and combinational logic optimization, minimization (subsections 1.1-1.4)

- 3. Sequential logic networks (subsection 3.2) with synchronous and asynchronous circuits

- 4. Microprocessor basics (Chapter 5) including memory structures (Chapter 4)

# Contents

| 1   | Fundamental Principles of Digital Logic              | 1  |

|-----|------------------------------------------------------|----|

| 1.1 | Boolean Algebra and its Relation to Digital Circuits | 3  |

| 1.2 | Truth Table and Basic Boolean Functions              | 7  |

| 1.3 | Boolean Expressions                                  | 9  |

| 1.4 | Minimization of Logic Functions                      | 13 |

| 1.5 | Combinational Logic Networks                         | 23 |

|     |                                                      |    |

| 2   | Number Systems                                       | 30 |

| 2.1 | Positional Number Systems                            | 30 |

| 2.2 | Binary Arithmetic                                    | 34 |

| 2.3 | Signed Binary Numbers                                | 38 |

| 2.4 | Binary Codes and Decimal Arithmetic                  | 40 |

| 2.5 | Functional Blocks                                    | 45 |

|     |                                                      |    |

| 3   | Logic circuits and Components                        | 56 |

|     |                                                      |    |

| 3.1 | Digital Electronic Circuits                          | 56 |

| 3.2 | Sequential Logic Networks                            | 60 |

| 3.3 | Flip-Flops                                           | 62 |

| 3.4 | Registers and Counters                               | 70 |

| 4   | Semiconductor Memories and Their Properties | 79 |

|-----|---------------------------------------------|----|

|     |                                             |    |

| 4.1 | Volatile Memories                           | 79 |

| 4.2 | Nonvolatile Memories                        | 83 |

| 4.3 | Memory Expansion                            | 86 |

|     |                                             |    |

| 5   | Microprocessors Basics                      | 89 |

|     |                                             |    |

| 5.1 | Basic Microcomputer Organization            | 89 |

| 5.2 | General Purpose Microprocessor              | 91 |

| 5.3 | Instruction Sets                            | 92 |

|     |                                             |    |

| Ref | erences                                     | 95 |

## Chapter 1

## **Fundamental Principles of Digital Logic**

In general a **signal** can be defined as a value or a change in the value of a physical quantity. The signal represents, transmits or stores the information. The two main types of signal encountered in practice are analog and digital.

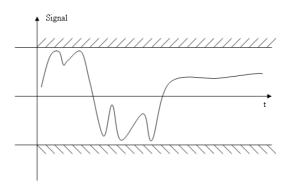

The **analog signal** is a continuous signal, which represents the information directly with its value. The time evolution of the analog signal can be represented by a continuous function. It changes continuously in time and it can cover fully a given range, see Figure 1.1. In practice the analog signal usually refers to electrical signals: especially voltage, but current, field strength, frequency etc. of the signal may also represent information.

For example, in sound recording, the voice (acoustic vibrations) is transformed by microphone (electro-acoustic transducer) into an electrical signal (voltage). Its characteristics are frequency range, signal-to-noise ratio, distortion, etc.

Analog circuits are designed for handling and processing analog signals and their input and output quantities are continuous. The advantages of such circuits are their ability to define infinite amounts of data, and they also use less bandwidth.

Figure 1.1 Analog signal

The analog signals have easy processing, which is made by analog circuits.

The primary disadvantage of analog signals and analog circuits is their noise sensitivity. As the signal is transmitted from source to a distant destination the unwanted noise and disturbance introduced by each step in the signal path deteriorates the signal quality.

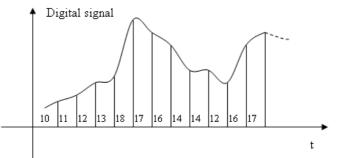

The **digital signal** contains the information in discrete symbols (e.g. numbers in coded form). It has discrete or quantized (the values of such a signal are restricted to belong to a finite set) values. The signal can be represented by integer numbers. One of the most common representations of a digital signal is the binary signal, which has a set of two elements: **0** and **1**.

The digital signal represents the information divided into elementary parts in a numeric form using appropriate encoding. Sampling is performed at given times, and the numbers are attached to it. The digital signal therefore represents coded information, see Figure 1. 2.

Figure 1.2 Digital signal

**Digital systems** manage discrete quantities of information; they are suitable for handling and processing digital signals. For example, a digital circuit is able to manipulate speech and music which are continuous (non-discrete) quantities of information. The signal is sampled at 8000 samples per second. Each sample is quantized and coded by a single byte. After these steps we have discrete quantity of information:

•The cost is 64 Kbit/s which is too much.

•Digital Signal Processing techniques allow us to bring this amount down to as low as 2.4 Kbit/s [1].

Digital systems are less expensive, with reliable operation, are easy to manipulate, are flexible, are immune to noise to a certain extent, etc.

Some disadvantages of digital circuits are the sampling of errors; digital communications require greater bandwidth than analog to transmit the same information.

Different data converters are the interfaces between analog devices and digital systems. In many applications it is need to convert an analog signal in a digital form suitable for processing by a digital system. An **analog-to-digital converter** (A/D) measures the analog signal at a certain rate and turns each sample into some bit values. The **digital-to-analog** (D/A) converters produce an analog output from a given digital input.

The next chapter introduces the basic principles of digital logic, and deals with the study of digital systems. The digital computer is the best known of such systems. Within a digital system the elementary units operate like switches, being either ON or OFF. The logic circuits can be built up from any basic unit that has two different states, one for the 1 input/output, and one for the 0 input/output. The complicated logic functions are the interconnection of a large number of switches called logic gates. The formal mathematical tool which can be used to describe the behaviour of logic networks is called Boolean algebra. In this chapter various types of Boolean algebra expressions will be introduced, and the description of logic connection and their implementation with various logic gates will be discussed.

### **1.1 Boolean Algebra and its Relation to Digital** Circuits

The operation of almost all modern digital computers is based on two-valued or binary systems. Propositions may be TRUE or FALSE, and are stated as functions of other propositions which are connected by the three basic logical connectives: AND, OR, and NOT. [2].

Boolean algebra was introduced in 1854 by George Boole in his book: An Investigation of the Laws of Thought [3]. The connection between Boolean algebra and switching circuits was established by Claude Shannon [4]. He introduced the so called switching algebra as a main analytical tool to analyze and design logic circuits and networks. Typically, the units are in the form of switches that can be either ON or OFF (mapping to transistor-switches; high voltage means logic 1 and low voltage means logic 0).

The binary logic systems use the Boolean algebra, as a mathematical system, defined on a set of two-valued elements, in which the values of variable are 1 and 0. The binary variables are connected through logic operations. Special elements of the set are the unity (its value is always 1) and the zero (its value is always 0). The binary/logic variables are typically represented as letters: A,B,C,...,X,Y,Z or a,b,c,...,x,y,z.

#### **Logic Variables**

Logic variables are used to describe the occurrence of events. It can have two values i.e. TRUE or FALSE or YES/NO which refers to the occurrence of an event. Their meaning corresponds to the everyday meaning of the words in question. TRUE corresponds to logic-1 and FALSE corresponds to logic-0. Here 1 and 0 are not digits; they do not have any numeric value.

The levels represent binary integers or logic levels of 1 and 0. In active-high logic, HIGH represents binary 1, and LOW represents binary 0. The meaning of HIGH/LOW is connected with the usual electrical representation of logic values, they correspond to high(er) and low(er) potentials (voltage levels) e.g. (nominally) +5 V and 0 V, respectively.

#### **Basic Boolean Operations**

There are several Boolean operations. The most important are:

- AND (conjunction) – represented by operators " $\cdot$ " or " $\wedge$ "

- OR (disjunction) – represented by operators "+" or " $\lor$ "

- NOT (negation, inversion, complementation) - represented by operator " $\neg$ " or denoted by overline (bar).

The AND and OR logic operations are two- or multi-variables, the logic negation is a one-variable operation.

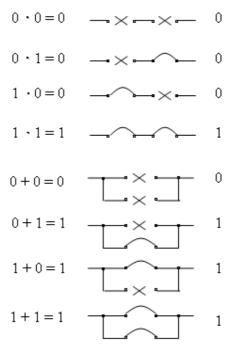

The result of AND operation is TRUE if and only if both input operands are TRUE. In logic algebra the AND operation is also called binary/logic multiplication. The AND operation between two variables A and B is written as A·B or AB. The postulates for the AND operation are given in Table 1.1.

| A |   | В |   | A·B |

|---|---|---|---|-----|

| 0 |   | 0 | = | 0   |

| 0 | • | 1 | = | 0   |

| 1 | · | 0 | = | 0   |

| 1 | • | 1 | = | 1   |

Table 1.1 Definition of the AND operation

The result of OR operation is TRUE if any input operands are TRUE. In logic algebra the OR operation is also called binary/logic addition. The OR operation

between two variables A and B is written as A+B. The postulates for the OR operation are given in Table 1.2.

| A |   | В |   | A+B |

|---|---|---|---|-----|

| 0 | + | 0 | = | 0   |

| 0 | + | 1 | = | 1   |

| 1 | + | 0 | = | 1   |

| 1 | + | 1 | = | 1   |

Table 1.2 Definition of the OR operation

Electrical implementation of AND and OR are series and parallel connection of switching elements (see Figure 1.3) like electromechanical relays or n-and p-channel FETs in CMOS circuitry (see Chapter 3).

Figure 1.3 Electrical implementation of the AND and OR operations

The result of NOT operation is TRUE if the single input value is FALSE. In this case the complementation of A is written as  $\overline{A}$ .

If A = 0; F =

$$\overline{A}$$

= 1 and if A = 1; F =  $\overline{A}$  = 0

$$\underbrace{\frac{A}{A}}_{0 \quad 1}$$

Table 1.3 Definition of the NOT operation

Each element of the set has its complementary also belonging to the set. A twovalued Boolean algebra is defined as a mathematical system with the elements 0 and 1 and three operations, whose postulates are given in Tables 1.1 to 1.3.

#### **Boolean Theorems**

Basic identities of Boolean algebra are presented in pairs i.e. with both AND and OR operations.

Let A be a Boolean variable and 0, 1 constants

| A + 0 = A; Zero Axiom;                                          | A + A = A; Idempotence                     |  |  |  |  |

|-----------------------------------------------------------------|--------------------------------------------|--|--|--|--|

| $A \cdot 1 = A$ ; Unit Axiom                                    | $A \cdot A = A$ ; Idempotence              |  |  |  |  |

| A + 1 = 1; Unit Property                                        | $A + \overline{A} = 1$ ; Complement        |  |  |  |  |

| $A \cdot 0 = 0$ ; Zero Property                                 | $A \cdot \overline{A} = 0$ ; Complement    |  |  |  |  |

|                                                                 | $\overline{\overline{A}} = A$ ; Involution |  |  |  |  |

| Let A, B and C Boolean variables                                |                                            |  |  |  |  |

| 1. Commutativity: the order of operan                           | ds can be reversed                         |  |  |  |  |

| $\mathbf{A} \cdot \mathbf{B} = \mathbf{B} \cdot \mathbf{A}$     |                                            |  |  |  |  |

| $\mathbf{A} + \mathbf{B} = \mathbf{B} + \mathbf{A}$             |                                            |  |  |  |  |

| 2. Associativity: the operands can be r                         | regrouped                                  |  |  |  |  |

| $A \cdot (B \cdot C) = (A \cdot B) \cdot C = A \cdot B \cdot C$ |                                            |  |  |  |  |

| A + (B + C) = (A + B) + C = A + B + C                           |                                            |  |  |  |  |

| The order of operations is given by the parentheses.            |                                            |  |  |  |  |

| 3. Distributivity: the operands can be                          | reordered                                  |  |  |  |  |

|                                                                 |                                            |  |  |  |  |

$\mathbf{A} \boldsymbol{\cdot} (\mathbf{B} + \mathbf{C}) = \mathbf{A} \boldsymbol{\cdot} \mathbf{B} + \mathbf{A} \boldsymbol{\cdot} \mathbf{C}$

$A + (B \cdot C) = (A + B) \cdot (A + C)$ Uniting theorem (absorption law)

$A \cdot (A + B) = A$  $A + A \cdot B = A$

These theorems are only valid in logic algebra, and they are not valid in the ordinary algebra! In the binary system is some kind of symmetry between the AND and OR operators which is called duality. Every equation has its dual pair which can be generate by replacing the AND operators with OR (and vice versa) and the constants 0 with 1s (and vice versa).

#### **De Morgan's Laws**

De Morgan's laws or theorems occupy an important place in Boolean algebra. De Morgan's theorems may be applied to the

- negation of a disjunction:  $\overline{A + B} = \overline{A} \cdot \overline{B}$

Since two variables are false, it's also false that either of them is true.

- negation of a conjunction:  $A \cdot B = A + B$

Since it is false that two variables together are true, at least one of them should be false. The De Morgan's theorem is an important tool in the analysis and synthesis of digital and logic circuits. Its generalization to several variables is stated below:

$\overline{\mathbf{A} + \mathbf{B} + \mathbf{C} + \dots} = \overline{\mathbf{A}} \cdot \overline{\mathbf{B}} \cdot \overline{\mathbf{C}} \cdot \dots$

$\overline{\mathbf{A} \cdot \mathbf{B} \cdot \mathbf{C} \cdot ...} = \overline{\mathbf{A}} + \overline{\mathbf{B}} + \overline{\mathbf{C}} + ...$

### **1.2 Truth Table and Basic Boolean Functions**

In order to describe the behavior and structure of a logic network it is necessary to express its output F as a function of the input variables A, B, C....

A Boolean function domain is a set of n-tuples of 0's and 1's, and the range is an element of the set  $\{0, 1\}$ . The values of the function are obtained by substituting logic-0 and logic-1 for the corresponding variables in the expression [4]. The **truth table** is a unique representation of a Boolean function which shows the binary value of the function for all possible combinations of the independent variables. In case of N variables, the truth table has N + 1 columns, and  $2^N$  rows, for all possible binary combinations for the variables. In general, a truth table consists of

- column for each input variable

- row for all possible input values

- column for resulting function value

For given N binary variable there exist  $2^{2^{N}}$  different Boolean functions of these N variables.

#### **One Variable Boolean Functions**

In case of one variable, there exist four Boolean functions.

The names of these functions and the truth table (Table 1.4) are given below:

- $F_0^{1} = 0$ function constant 0

- function inversion (NOT)

- function identity

$F_1^{1} = \overline{A}$   $F_2^{1} = A$   $F_3^{1} = 1$ function constant 1

| А | F <sub>o</sub> <sup>1</sup> | $F_1^{1}$ | $F_2^1$ | $F_{3}^{1}$ |

|---|-----------------------------|-----------|---------|-------------|

| 0 | 0                           | 1         | 0       | 1           |

| 1 | 0                           | 0         | 1       | 1           |

Table 1.4 Truth table - one variable Boolean functions

#### **Two Variable Boolean Functions**

In the case of two variables the number of possible input combinations is  $2^2 = 4$ , therefore the number of possible two-variable functions is  $2^4 = 16$ . Each function describes a single or complex logic operation, see Table 1.5.

| Α | В | $F_0^{2}$ | $F_1^{2}$ | $F_2^{2}$ | $F_{3}^{2}$ | $F_{4}^{2}$ | $F_{5}^{2}$ | $F_{6}^{2}$ | $F_{7}^{2}$ | $F_{8}^{2}$ | $F_{9}^{2}$ | $F_{10}^{2}$ | $F_{11}^{2}$ | $F_{12}^{2}$ | $F_{13}^{2}$ | $F_{14}^{2}$ | $F_{15}^{2}$ |

|---|---|-----------|-----------|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 0 | 0 | 0         | 0         | 0         | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 1            | 1            | 1            | 1            | 1            | 1            |

| 0 | 1 | 0         | 0         | 0         | 0           | 1           | 1           | 1           | 1           | 0           | 0           | 0            | 0            | 1            | 1            | 1            | 1            |

| 1 | 0 | 0         | 0         | 1         | 1           | 0           | 0           | 1           | 1           | 0           | 0           | 1            | 1            | 0            | 0            | 1            | 1            |

| 1 | 1 | 0         | 1         | 0         | 1           | 0           | 1           | 0           | 1           | 0           | 1           | 0            | 1            | 0            | 1            | 0            | 1            |

| Table 1.5 Truth table - two | variables Boolean functions |

|-----------------------------|-----------------------------|

|-----------------------------|-----------------------------|

| function constant 0                        |

|--------------------------------------------|

| function AND                               |

| function inhibition                        |

| function identity                          |

| function inhibition                        |

| function identity                          |

| function antivalency, exclusive-OR         |

| (XOR)                                      |

| function OR                                |

| function NOR                               |

| function equivalency, exclusive-NOR (XNOR) |

| function inversion                         |

| function implication                       |

| function inversion                         |

| function implication                       |

| function NAND                              |

| function constant 1                        |

|                                            |

A logic function can be specified in various ways:

1. Truth table

2. Boolean equation, algebraic form

3. Maps (see subsection 1.4)

4. Symbolic representation, logic gates (see subsection 1.5)

The conversion of one representation of a Boolean function into another is possible in a systematic way.

# **1.3 Boolean Expressions**

#### Obtaining a Boolean expression from a truth table

In the next example a Boolean expression of three variables is obtained from a truth table, see Table 1.6.

The logic expression is a function (formula) consisting of Boolean constants and variables connected by AND, OR, and NOT operations. The expression is:  $F = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

| i | A $(2^2)$ | $B(2^{1})$ | $C(2^{0})$ | F |

|---|-----------|------------|------------|---|

| 0 | 0         | 0          | 0          | 0 |

| 1 | 0         | 0          | 1          | 1 |

| 2 | 0         | 1          | 0          | 1 |

| 3 | 0         | 1          | 1          | 0 |

| 4 | 1         | 0          | 0          | 0 |

| 5 | 1         | 0          | 1          | 1 |

| 6 | 1         | 1          | 0          | 1 |

| 7 | 1         | 1          | 1          | 0 |

Table 1.6 Truth table for the Boolean expression

Each term represents an input variable combination for which the function value is F = 1, consisting of all variables either in negated or in unnegated form.

#### Sum-of-Products (SOP) Form, the Minterm Canonical Form

The unique algebraic form readout from the truth table as AND connections of OR operations is called **Sum-of-Products (SOP) form, disjunctive canonical form**, **disjunctive normal form** (DNF) or **minterm canonical form**.

#### Minterm

The minterm is a term composed from the variables logic product, in which all the variables appear exactly once, either complemented or uncomplemented. The terms of the disjunctive canonic form are called minterm [5]. There are  $2^{N}$  distinct minterms for N variables.

The generalized form is denoted by:  $m_i^N$

where N is the number of independent variables, and **i** (minterm index) is the decimal value of the binary number corresponding to the given combination of the independent variables.

To illustrate the notation, consider the previous function expression

$F = \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} + A\overline{B}\overline{C}$

$$F = m_1^3 + m_2^3 + m_5^3 + m_6^3 = \sum_{1}^{3} (1, 2, 5, 6)$$

#### Product-of-Sums (POS) Form, Maxterm Canonical Form

The unique algebraic form readout from the truth table as OR connections of AND operations is called **Product-of-Sums (POS) form, conjunctive canonical form, conjunctive normal form** (CNF) or **maxterm canonical form**.

#### Maxterm

There is a dual entity called maxterm which is a product of sums expansion (conjunctive normal form). The maxterm is a term composed from the variables logic sum, in which all the variables appear exactly once, either complemented or uncomplemented. There are  $2^{N}$  distinct maxterms for N variables [5].

The generalized form is denoted by:  $M_{I}^{N}$

where N is the number of independent variables, and I (maxterm index) is the decimal value of the binary number corresponding to the given combination of the independent variables.

To find the conjunctive canonic form, we consider the negated function from Table 1.6 (see rows nr. 0, 3, 4, 7)

$$F(A, B, C) = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + ABC$$

$$\overline{F} = m_0^3 + m_3^3 + m_4^3 + m_7^3$$

Based on De Morgan's law the conjunctive canonical form of function F can be obtained from the negated function expression by appropriate transformations resulting in a product-of-sums (POS) i.e. in a product of maxterms. The complemented function consists of those minterms, where the function value is F = 0.

$$F(A, B, C) = \overline{F(A, B, C)} = \overline{ABC} + \overline{ABC} + \overline{ABC} + A\overline{BC} + ABC = (A + B + C)(A + \overline{B} + \overline{C})(\overline{A} + B + C)(\overline{A} + \overline{B} + \overline{C})$$

$$\mathbf{F} = \mathbf{M}_{7}^{3} \cdot \mathbf{M}_{4}^{3} \cdot \mathbf{M}_{3}^{3} \cdot \mathbf{M}_{0}^{3} = \prod^{3} (7, 4, 3, 0)$$

#### Minterm to Maxterm Conversion

Let's start from the original function disjunctive normal form

$$F = m_1^3 + m_2^3 + m_5^3 + m_6^3$$

The expression of the negated function, also in disjunctive form (index i) is

$$\overline{F} = m_0^3 + m_3^3 + m_4^3 + m_7^3$$

The function expression in conjunctive normal form, (index  $I = 2^3 - 1 - i$ ) is

$$\mathbf{F} = \mathbf{M}_7^3 \cdot \mathbf{M}_4^3 \cdot \mathbf{M}_3^3 \cdot \mathbf{M}_0^3$$

The relationship between the minterm indexes **i** of the complemented function and the maxterm **I** of the uncomplemented function (written for the case of three variables) is  $i + I = 7 = 2^3 - 1$

In general, we can write for a function with N variables

$$i + I = 2^{N} - 1$$

We can state that: all minterm is the complement of a maxterm and vice versa.

$$\overline{m^n_{_i}} = M^n_{2^N\text{-}1\text{-}i} \text{ and } M^n_i = \overline{m^n_{_{2^N\text{-}1\text{-}i}}}$$

The sum of all the minterms of an N variable function is 1, the product of all the maxterms is 0.

$$\sum_{i=0}^{2^{N}-1} m_{i}^{n} = 1 \text{ and } \prod_{i=0}^{2^{N}-1} M_{2^{N}-1-i}^{n} = 0$$

## **1.4** Minimization of Logic Functions

The logic functions are used to design digital logic circuits. The aim is to find an economic, small, fast and cheap implementation of the specified logic network. In many cases the optimization, simplification of the network means to reduce the number of electronic components, the number of gates level, the number of inputs-, interconnections etc. Since the expressions resulting from simplification are equivalent, the logic networks that they describe will be the same.

Boolean function simplification methods are:

- Algebraic minimization, using Boolean algebraic transformations

- Graphic minimization, using the Karnaugh-map

- Numeric (tabular) minimization, using Quine-McCluskey- method.

- Heuristic algorithms, (e.g. algorithms like ESPRESSO).

In the next the first two methods will be discussed in detail.

#### Algebraic minimization using Boolean theorems

The laws and identities of Boolean algebra allow us to simplify a minterm expression. A significant simplification of minterms yields to an equivalent new function expression with fewer Boolean operators and variables. Unfortunately, with this procedure it could be difficult to find the "simplest" expression because the Boolean expressions are not algorithmic. Hence, it is not always obvious which theorem to apply at each step. During algebraic minimization, systematically, the basic properties and theorems of Boolean algebra had to be applied. In this way, step by step the adjacent minterms (differing by ONLY one variable, which appears complemented in one term and uncomplemented in the other) are contacted, and the corresponding variables are eliminated.

For example, to simplify the function

$$F = \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} + A\overline{B}\overline{C}$$

we can proceed as follows:

$$F = \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} + A\overline{B}\overline{C} = \overline{B}C(\overline{A} + A) + \overline{B}\overline{C}(\overline{A} + A)$$

$$= \overline{B}C + \overline{B}\overline{C}$$

A similar approach can be applied to the conjunctive form, adjacent maxterms are contacted, and the corresponding variables are eliminated. For example, to simplify the function

$$F = \left(A + B + \overline{C}\right) \left(A + \overline{B} + \overline{C}\right)$$

we can proceed as follows:

$$F = (A + B + \overline{C})(A + \overline{B} + \overline{C}) = ((A + \overline{C}) + B)((A + \overline{C}) + \overline{B})$$

$$= (A + \overline{C}) + (B + \overline{B})(A + \overline{C}) + B \overline{B}$$

$$= A + \overline{C}$$

#### Graphic minimization, Karnaugh map (K-map)

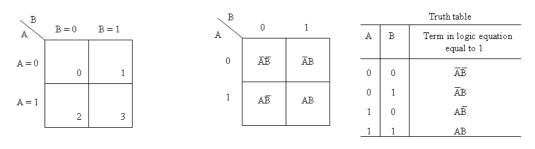

**Karnaugh maps** were invented by Maurice Karnaugh, a telecommunications engineer. He developed them at Bell Labs in 1953 while studying the application of digital logic to the design of telephone circuits. This method is typically used on Boolean functions of two, three or four variables - past that, other techniques are frequently used. [4].

The Karnaugh map, known also as Veitch diagram, is a unique graphic representation of Boolean functions which provides a technique for the logic equation minimalization. The array of cells contains the truth table information. Mapping can be applied both to minterms and maxterms as well. The K-map of a Boolean function of N variables consists of  $2^{N}$  cells and is built up from adjacent cells having terms which differ only in one bit (place) [6]. Adjacent terms are where only **one** logic variable appears in complemented and uncomplemented form, while all others remain the same. For example: (011) and (010), also (000) and (100)

This arrangement allows a quick and easy simplification keeping some simple rules. In the case of 5 or more variables the adjacent cells scheme becomes much more complex.

#### **Minimal Sums**

One method of obtaining a Boolean expression from a K-map is to select only those minterms of the normal expression that have a logic-1 value.

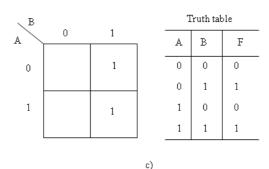

#### **Two Variable Karnaugh Maps**

The two-variable K-map contains four cells, covering all possible combinations of the two variables as is shown in Figure 1.4. Each row of the truth table corresponds to exactly one cell. If the truth table row is **one** the respective cell contains a **one**. Usually the zeros are not indicated, and an empty cell is considered to contain a **zero**. Figure 1.4 a presents also the numbering of K-maps cells. Figure 1.4 c shows a two variable logic function truth table and the corresponding K-map. The logic function would be 1 if

A = 0 AND B = 1 OR A = 1 AND B = 1.

If the row or column of the map in which the **1** appears is labeled by a **1**, the variable appears uncomplemented, otherwise the variable appears complemented. Read through the K-map cells content, the function expression is:  $F = \overline{AB} + AB$

b)

Figure 1.4 Karnaugh maps: a) two-variable map; b) correspondence with truth table; c)example

Using the algebraic minimization, the function can be rewritten as:  $F = \overline{AB} + AB = (\overline{A} + A)B = B$  The K-map advantage is that the adjacent cells (which differ by ONLY one variable, appear complemented in one cell and uncomplemented in the other) can be grouped visually to eliminate redundant variables. Thus, grouping of the two cells, see Figure 1.5, immediately we obtain the simplified function form.

Figure 1.5 Karnaugh map; F = B

#### **Three - Variable Karnaugh Maps**

The K-maps edges are headed using a one-step (Gray) code.

The **Gray code** is a series of  $2^{N}$  code words, each of N-bits, in such a sequence that any adjacent code words differ only in one bit, including the first and last words too (cyclic property).

For example, in case of N = 2 the sequence of code words is:

(00), (01), (11), (01)

The **Hamming distance** of two code words of equal length is the number of positions at which the corresponding codes are different. For example, 10110 and 01101 differ in 4 positions, the distance between them is 4.The Hamming distance between any two adjacent code words of the Gray code is one (see Table 2.4).

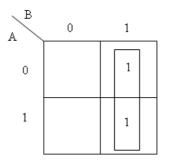

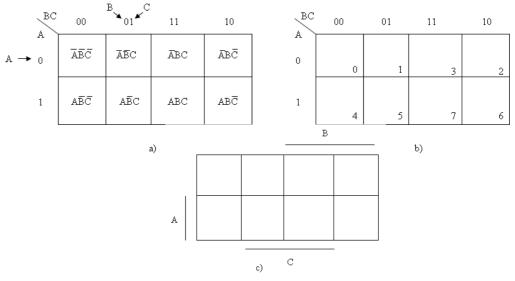

When K-maps involve three variables; the cells represent the minterms of all variables, as is shown in Figure 1.6 a. The numbering of K-maps cells is presented in Figure 1.6 b. In Figure 1.6 c those columns and row are signed where the corresponding variables have logic-1 value.

Top cells are adjacent to bottom cells. Left-edge cells are adjacent to right-edge cells. Rows and columns on the opposite sides are also adjacent.

In the process of contraction and minimization the following steps and rules are necessary:

- introduce **ones** in each cell of the K-map for which the corresponding minterm in the function is equal to **one**.

- group adjacent cells which contain **ones**. The number of cells in a group must be a power of 2.

- the process is continued until no more variables can be eliminated by further contractions. The groups cover all cells containing **ones**.

Figure 1.6 Three-variable Karnaugh maps

In the case of three variables K-map:

- If a group of four adjacent cells (in-line or square) is contracted, the result yields in a single variable.

- If a group of two adjacent cells is contracted, the result yields in a two-variable product term.

- A single cell which cannot be combined represents a three-variable term.

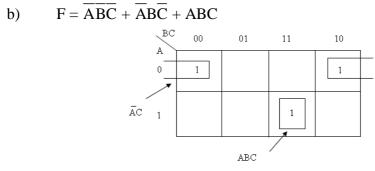

**Example 1.1** Use the K-Map to simplify the following expression:

a)  $F = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$ ; (Truth table, see Table 1.6)

The map is shown in Figure 1.7, and the indicated grouping leads to the simplified expression

$F = \overline{B}C + B\overline{C}$

Figure 1.7 Karnaugh map for Example 1.1 a

Figure 1.8 Karnaugh map for Example 1.1 b

Figure 1.8 shows a split rectangular grouping and a single cell which cannot be combined (represents a three-variable term). The simplified expression is:

$$F = \overline{AC} + ABC$$

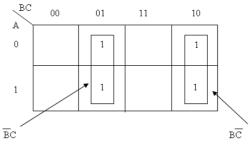

In Figure 1.9 the optimal grouping of 1-cells are shown. The minimal sums for K maps are given.

Figure 1.9 Grouping on three-variable Karnaugh maps

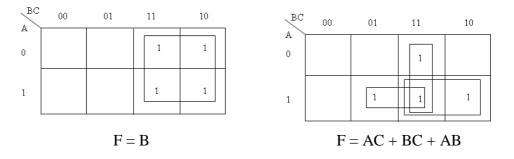

#### Four-Variable Karnaugh Maps

A four-variable map has 16 cells, as shown in Figure 1.10. The grouping rules are the same as for three variables K map. The goal is to find the smallest number of the largest possible sub cubes that cover the 1-cells.

Figure 1.10 Four-variable Karnaugh maps

**Example 1.2** Use the K-map to simplify the logic function given by the minterms

$$F = \sum_{i=1}^{4} (0, 2, 5, 8, 9, 10, 11, 12, 13, 14, 15)$$

The corresponding Karnaugh map is given in Figure 1.11.

Figure 1.11 Karnaugh map for Example 1.2

The simplified expression is

$F = A + B\overline{C}D + \overline{B}\overline{D}$

The obtained terms are called the function **prime implicants**. If a minterm of a function is included in only one prime implicant, then this prime implicant is an **essential prime implicant** of the function [7].

In this way the K-maps permit the rapid identification and elimination of potential race hazards. The simplification result may not be unique.

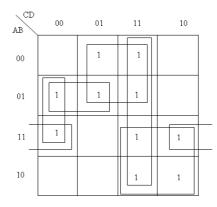

**Example 1.3** Simplify the Karnaugh-map shown in Figure 1.12.

Figure 1.12 Karnaugh map for Example 1.3

The simplification result consists of 6 prime implicants:

$F = \overline{A}D + CD + AC + AB\overline{D} + B\overline{C}\overline{D} + \overline{A}B\overline{C}$

Essential prime implicants for minimum cover

$F = \overline{A}D + AC + B\overline{C}\overline{D}$

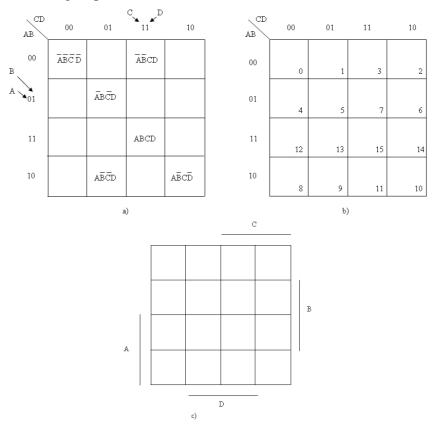

#### Karnaugh Map for Minimalization of a Four Variables Logic Function Expressed in Product-Of-Sums

Sometimes the Product-Of-Sums form of a function is simpler than the Sum-of Product form. In a very similar way as in the previous subsection (Four-Variable Karnaugh Maps), two adjacent maxterms can be contracted to a single sum. The involution identity is applied for the logic function:  $\overline{\overline{F}} = F$ . In the minterm K-map the simplifications are made using zeros, obtaining the minimalization of  $\overline{F}$ .

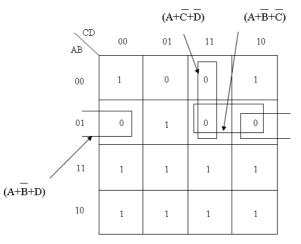

**Example 1.4** K-map method: contracting zeros (second "optimum" solution for the function given in Example 1.2)

Use the - map to simplify the logic function given by the minterms

$$\mathbf{F} = \sum_{i=1}^{4} (0, 2, 5, 8 - 15)$$

The corresponding Karnaugh-map is given in Figure 1.13.

In the next the following rule is used: Replace F by  $\overline{F}$ , and 0's become 1's and vice versa.

$$\overline{F} = \overline{A}B\overline{D} + \overline{A}BC + \overline{A}CD$$

$$F = \overline{\overline{F}} = \overline{\overline{A}}B\overline{\overline{D}} + \overline{\overline{A}}B\overline{C} + \overline{\overline{A}}C\overline{D}$$

$$F = (A + \overline{B} + D)(A + \overline{B} + \overline{C})(A + \overline{C} + \overline{D})$$

Figure 1.13 Karnaugh map for Example 1.4

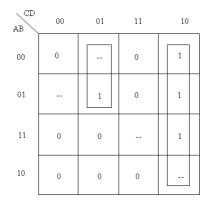

#### **Incompletely Specified Logic Function**

In the expression of incompletely specified logic function are such input combinations to which the Boolean function is not specified. The function value for these combinations is called **don't care** and the combination is called don't care condition.

In an implementation the don't care terms value may be arbitrarily 0 or 1. The selection point of view is if they are able to generate prime implicants in order to obtain the most advantageous solution.

Don't care conditions are indicated on the K- maps by dash entries. Figure 1.14 shows a Karnaugh map involving don't care conditions.

Figure 1.14 Karnaugh map with don't care conditions

The map of Figure 1.14 can be used to obtain a minimal sum:

$\mathbf{F} = \overline{\mathbf{A}}\overline{\mathbf{C}}\mathbf{D} + \mathbf{C}\overline{\mathbf{D}}$

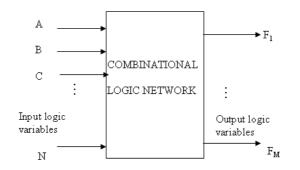

### **1.5** Combinational Logic Networks

Logic networks are implemented with digital circuits, and in reverse, digital circuits can be described and modeled with logic networks. For the analysis and synthesis of logic network the Boolean algebra is used.

The logic network (logic circuit) processes the actual values of the input variables (A, B, C, ...) and produces accordingly the output logic functions  $(F_1, F_2, ...)$ .

Logic networks described by truth tables or Boolean expressions can be classified into two main groups:

1. Combinational networks: the output values depend only on the present input variable values;

2. Sequential networks: the output values depend on both the inputs to the operation and the result of the previous operation. Networks having the memory property will be studied in subsection 3.2.

The combinational logic network is the simplest logic network. The logic operations on the input variables are performed "instantaneously" and the result will be available on the output at the same time, (except for the time delay due to the internal operation of the circuits). The output variables can be represented as logic functions of the input variables. Figure 1.15 shows a combinational logic network as a black box.

$F_i = f(A, B, C, ..., N)$  i = 1, 2, ..., M

Figure 1.15 Combinational logic network

The combinational circuit maps an input (signal) combination to an output (signal) combination. The same input combination always implies the same output combination (except transients). The reverse is not true. For a given output combination different input combinations can belong.

Combinational circuit examples: binary arithmetic circuits (half-adder, fulladder, etc.) (see subsection 2.2), binary-coded-decimal code (BCD) – seven segment display (see subsection 2.4), various encoders and decoders, multiplexers and demultiplexers, comparators (see subsection 2.5), etc.

The combinational circuits are the interconnections of a large number of switches called logic gates.

#### **Logic Gates**

Logic gates as electronic circuit components are elementary building blocks of logic circuits which implement basic Boolean functions of one or more variables.

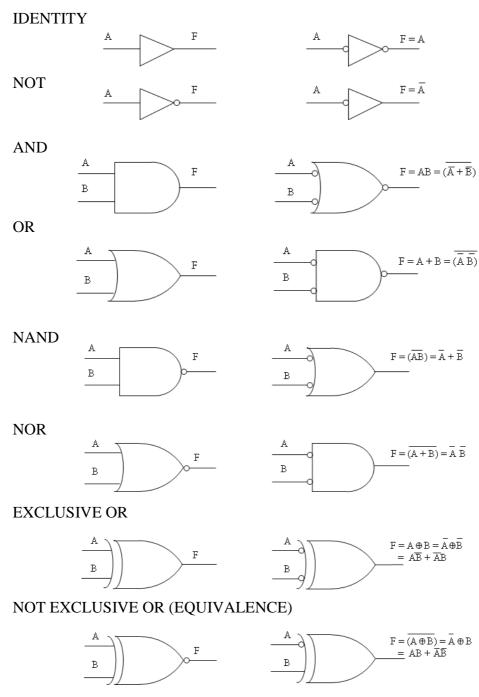

Figure 1.16 lists the symbols of the main logic gates with two inputs. The NOT gate implements the function inversion, having one input. A simple triangle symbol denotes a buffer amplifier, which serves the IDENTITY function. The small circle on the input or output of a gate means the NOT operation. Based on De Morgan's identities:

$$F = AB = \left(\overline{\overline{A} + \overline{B}}\right)$$

and  $F = A + B = \left(\overline{\overline{A} \ \overline{B}}\right)$

While the NOT, AND, OR functions have been designed as individual circuits in many circuit families, by far the most common functions realized as individual circuits are the AND-NOT (NAND) and OR-NOT (NOR) circuits. A NAND can be described as equivalent to an AND element driving a NOT element. Similarly, a NOR is equivalent to an OR element driving a NOT element. The reason for this strong bias favoring inverting outputs is that the transistors which preceded it are by nature inverters or NOT-type devices when used as signal amplifiers.

Figure 1.16 Main gate symbols

#### The EXCLUSIVE OR and NOT EXCLUSIVE OR Functions

The final two gates symbols introduced in Figure 1.16 are the EXCLUSIVE OR gate and the NOT EXCLUSIVE OR (Equality) gate. The EXCLUSIVE OR, (XOR) called the modulo-2-sum or "antivalency" operation is denoted by the symbol  $\oplus$ . The EXCLUSIVE OR function forms are:

$F = A \oplus B = \overline{A}B + A\overline{B}$  $F = \overline{A} \oplus \overline{B} = \overline{\overline{A}}\overline{B} + \overline{\overline{A}}\overline{\overline{B}}$

By definition the value of  $A \oplus B$  is logic-1 if and only if A and B variables have different values. The complement of the EXCLUSIVE OR operation is the NOT EXCLUSIVE OR (called EXCLUSIVE NOR, XNOR or "equivalency") operation. Their expressions are:

$F = (\overline{A \oplus B}) = \overline{\overline{AB} + A\overline{B}} = (\overline{\overline{AB}}) (\overline{A\overline{B}}) = (A + \overline{B})(\overline{A} + B) =$  $= A\overline{A} + AB + \overline{B}\overline{A} + \overline{B}B = AB + \overline{A}\overline{B}$  $F = \overline{A} \oplus B = \overline{\overline{AB}} + \overline{\overline{AB}}$

By definition the value of  $A \oplus B$  is logic-1 if and only if A and B variables have the same values. The EXCLUSIVE OR and NOT EXCLUSIVE OR gates are typically available with only two inputs.

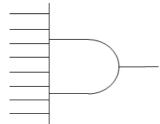

The commercial gates (exception NOT) are often designed for multiple inputs. Generalized symbol shown in Figure 1.17 is frequently used when a single gate has several inputs.

Figure 1.17 AND gate with 8 inputs

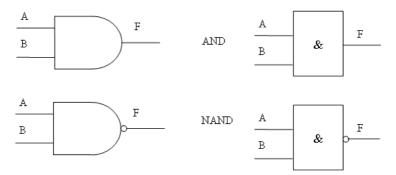

The IEEE standard specifies two different types of symbols for logic gates [8]: the distinctive- and rectangular-shape symbols. Figure 1.16 shows the main distinctive-shape symbols and Figure 1.18 compares the AND and NAND gate symbols. Both of them are frequently used and the standard says that it has no preference between them. Since most digital designers and computer-aided design (CAD) systems prefer the distinctive-shape symbols, these symbols are used in this book.

Figure 1.18 Example for distinctive- and rectangular shape logic symbols

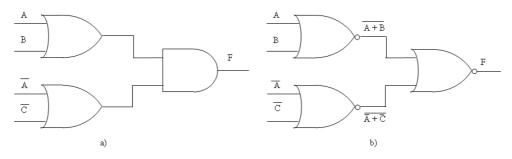

#### Standard Forms for Logic Functions, Synthesis Using Standard Expressions and the Corresponding Circuits with NAND or NOR Gates

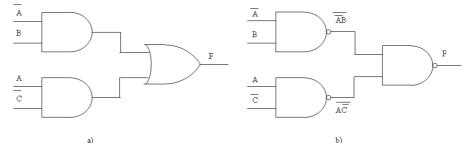

All logic functions can be specified using AND, OR and NOT operations. Both canonical forms: Sum of Products (SOP) and Product of Sums (POS) can specified and implemented by two-level AND-OR or OR-AND gate networks, respectively. Because the AND, OR and NOT operations can be implemented using either only NAND or only NOR gates, then based on the respective canonical forms all logic functions can be implemented with homogeneous two-level NAND or NOR gate networks. Consider the sum-of-products expression:

$F = \overline{A}B + A\overline{C}$

The two-level AND-OR circuit consists of a number of AND gates equal to the number of terms followed by a single OR gate. The logic circuit is shown in Figure 1.19 a. Next we apply De Morgan's theorem to the above function

$$\overline{F} = \overline{\overline{A}B + A\overline{\overline{C}}} = (\overline{\overline{A}B}) \ (\overline{A\overline{\overline{C}}})$$

and therefore  $F = \overline{\overline{F}} = (\overline{\overline{AB}}) (\overline{AC})$ . The corresponding circuit with NAND gates is shown in Figure 1.19 b.

Figure 1.19 a) AND-OR circuit; b) corresponding circuit with NAND only

Although, the expression  $F = \overline{F} = (\overline{\overline{AB}}) (\overline{AC})$  looks more complicated than  $F = \overline{AB} + \overline{AC}$ , the circuit built up from NAND gates (Figure 1.19 b) has the advantage that is built up from the same gate types and consists of less transistors. If we start with a product-of-sums expression, the resulting circuit will be a two-level OR-AND structure. If the POS expression is:

$$\mathbf{F} = (\mathbf{A} + \mathbf{B}) \ (\overline{\mathbf{A}} + \overline{\mathbf{C}})$$

Using De Morgan's theorems, we can transform the expression as follows:

$$\overline{\overline{F}} = \overline{(\overline{A} + B) (\overline{\overline{A}} + \overline{\overline{C}})} = \overline{(\overline{A} + B)} + \overline{(\overline{\overline{A}} + \overline{\overline{C}})}$$

Hence  $\overline{F} = \overline{\overline{F}} = \overline{\overline{(\overline{A} + B)} + \overline{(\overline{\overline{A}} + \overline{\overline{C}})}}$

The POS function two-level OR-AND structure and the corresponding NOR circuit is shown in Figure 1.20.

Figure 1.20 a) OR-AND circuit; b) corresponding circuit with NOR only

### Problems

1.1 Simplify the following expressions as far as possible:

- a)  $F_1 = A\overline{B}\overline{C}D + A\overline{B}CD + A\overline{B}C\overline{D} + A\overline{B}C\overline{D}$

- b)  $F_2 = AB + A\overline{B} + ABC\overline{D}$

- c)  $F_3 = \overline{ABC} + \overline{A+B+C}$

1.2 For three logic variables prove the identity:

$\mathbf{F} = \mathbf{A} \oplus \mathbf{B} \oplus \overline{\mathbf{C}} = \overline{\mathbf{A} \oplus \mathbf{B} \oplus \mathbf{C}}$

- 1.3 Evaluate the following expressions for A = B = C = 1; D = 0; E = 1

- a)  $(\overline{AB} + A\overline{B}) + (\overline{B} + C)D\overline{E}$

- b)  $\overline{A}(B + E) + AB\overline{C}\overline{D}$

- c)  $AB(\overline{\overline{C} + E}) + \overline{B}(D + \overline{E})$

1.4 Convert the EXCLUSIVE OR function into NAND form and show the corresponding circuit.

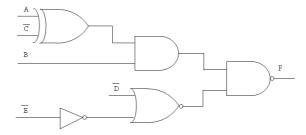

1.5 Write a Boolean expression for the logic diagram shown below:

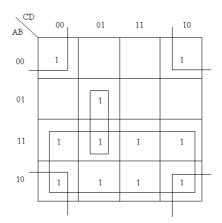

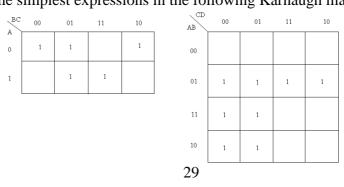

1.6 Find the simplest expressions in the following Karnaugh maps:

## Chapter 2

# **Number Systems**

In digital computers the information is represented in a string of ON and OFF states of logic variables, a series of logic-1s and logic-0s. This chapter covers the positional number systems (decimal, binary, octal, and hexadecimal), the number conversions, representations of integer and real numbers and arithmetic operations. Various codes and the code conversion are studied. Finally, encoders, decoders, multiplexers, demultiplexers and various comparators are discussed.

### 2.1 Positional Number Systems

In the positional number system, or so called radix-weighted positional number system the value of a number is a weighted sum of its digits. The value associated with a digit is dependent on its position. In general, the numbers, in the base r (radix) system are of the form:

$N = a_{j}r^{j} + a_{j-1}r^{j-1} + ... + a_{1}r^{1} + a_{0}r^{0} + a_{-1}r^{-1} + ... + a_{-k}r^{-k}$ Where: *r* is the base of the number system, *j*, *j*-1,...,-(*k*-1),-*k* scalars,  $a_{j}, a_{j-1}, ..., a_{1}, a_{0}, a_{-1}, ..., a_{k}$  natural numbers between 0 and *r* - 1, inclusive.

#### **Decimal Number System**

The well known decimal system is just one in the class of number systems which belongs to the weighted positional number system. The decimal system is the most commonly used in our daily arithmetic. The numbers in combination of 10 symbols (digits) are called the decimal number system. This is a grouping system based on the repetition of symbols to note the number of each power of the base, in this case 10. The distinct digits (0 – 9) are multiplied by the power of 10, and it is significant that the position occupied by each digit. "." is called the radix point. In the case of decimal number 356.21:

$N = 356.21 = (3 \times 10^{2}) + (5 \times 10^{1}) + (6 \times 10^{0}) + (2 \times 10^{-1}) + (1 \times 10^{-2})$

#### **Binary Number System**

In the binary system, the base is 2 (r = 2) and the symbols are 0 and 1. These numbers in positional code are expressed as power series of 2, and are called bits (binary digit).

In the expression  $N = a_i r^j + a_{i-1} r^{j-1} + ... + a_1 r^1 + a_0 r^0 + a_{-1} r^{-1} + ... + a_{-k} r^{-k}$

$a_i$  denotes the most significant bit (MSB);

$a_{-k}$  denotes the least significant bit (LSB)

#### Conversion from binary to decimal

For example, consider the binary number 1101.01. This is expanded as:  $1101.01_2 = (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) + (0 \times 2^{-1}) + (1 \times 2^{-2})$  $= 8 + 4 + 1 + 0.25 = 13.25_{10}$

#### Conversion from decimal to binary

Several methods exist to convert from decimal to binary and vice versa. In the next two methods are presented:

Method 1 Descending Powers of Two and Subtraction

For numbers less then thousands, this method offers a very rapid and easy technique. The steps are:

- Find the greatest power of 2 that is close and less than the decimal number, and after that calculate the difference between them.

- Choose a next (lower) power of 2 which is close and less than the subtraction result.

- Repeat the above mentioned operations until the sum of the powers of 2 will give the decimal number. The binary answer is composed from 1s in the positions where the power of 2 fit into the decimal number and 0s otherwise.

For example, find the 156 decimal number binary equivalents. We list the power of 2 s and we "build" the corresponding number.

| 2 <sup>8</sup> | 2 <sup>7</sup><br>128<br>1 | 2 <sup>6</sup> | $2^{5}$ | $2^4$ | $2^{3}$ | $2^{2}$ | $2^{1}$ | $2^{0}$ |

|----------------|----------------------------|----------------|---------|-------|---------|---------|---------|---------|

| 256            | 128                        | 64             | 32      | 16    | 8       | 4       | 2       | 1       |

| 0              | 1                          | 0              | 0       | 1     | 1       | 1       | 0       | 0       |

#### Method 2 Division by Two with Remainder

If the number has a radix point, as a first step, it is important to separate the number into an integer and a fraction part, because the two parts have to be converted differently.

The conversion of a decimal integer part to a binary number is done by dividing the integer part to 2 and then writing the remainders (0 or 1). Proceed with all successive quotients the same way and accumulate the remainders. For example, find the 56 decimal number binary equivalent:

| Number divided by 2 | Result | Remainder |     |   |  |  |

|---------------------|--------|-----------|-----|---|--|--|

| 56/2                | 28     | 0         | LSB | • |  |  |

| 28/2                | 14     | 0         |     |   |  |  |

| 14/2                | 7      | 0         |     |   |  |  |

| 7/2                 | 3      | 1         |     |   |  |  |

| 3/2                 | 1      | 1         |     |   |  |  |

| 1/2                 | 0      | 1         | MSB |   |  |  |

$56_{10} = 111000_2$

The conversion of a decimal fraction part to a binary number is done by multiplying the fractional parts by 2 and accumulating integers.

For example, find the 0.6875 decimal number binary equivalent:

| Number multiplying by 2 | Integer | Result |

|-------------------------|---------|--------|

| 0.6875 x 2 =            | 1       | 0.3750 |

| 0.3750 x 2 =            | 0       | 0.7500 |

| 0.7500 x 2 =            | 1       | 0.5000 |

| 0.5000 x 2 =            | 1       | 0.0000 |

$0.6875_{10} = 0.1011_2$ And  $56.6875_{10} = 111000.1011_2$

#### **Octal and Hexadecimal Numbers**

Positional number systems with base 8 (octal) and base 16 (hexadecimal) are used in digital computers.

In octal system the eight required digits are 0 to 7, and the radix is 8. The hexadecimal system (base 16) uses sixteen distinct symbols: numbers from 0 to 9, and letters A, B, C, D, E, F to represent values between ten to fifteen.

#### Conversion from octal or hexadecimal to decimal

The conversion is similar to the previous subsection Method 2. This approach is called: Division by Eight or Sixteen with Remainder. Here the numbers in the positional code are expressed as power series of 8 and 16.

For example:

$327_8 = 3 \times 8^2 + 2 \times 8^1 + 7 \times 8^0 = 215_{10}$

## Conversion from octal and hexadecimal to binary

For example, to convert from binary to octal, the binary number three bit groups were separated, that could be converted directly:

| 011<br>3 | 010<br>2 | 111<br>7 | 001<br>1 | binary number<br>octal equivalent |

|----------|----------|----------|----------|-----------------------------------|

| Vice     | versa:   |          |          |                                   |

| 4        | 5        | 6        | 2        |                                   |

| 100      | 101      | 110      | 010      |                                   |

To convert from hexadecimal to binary and reverse, the binary number four bit groups were separated, that could be converted directly:

1010 0010  $1101_2 = A2D_{16}$

$7F3_{16} = 0111 \ 1111 \ 0011_2$

The **non-positional number systems** uses for example Roman numerals (I = 1, V = 5, X = 10, L = 50, C = 100, D = 500 and M = 1000).

# 2.2 Binary Arithmetic

Arithmetic operations with numbers in base r follow the same rules as for decimal numbers. The addition, subtraction, multiplication and division can be done in any radix-weighted positional number system.

In digital computers arithmetic operations are performed with the binary number system (radix = 2). The binary system has several mathematical advantages: i.e. easy to perform arithmetic operations and simple to make logical decisions. The same symbols (0 and 1) are used of arithmetic and logic. Now we will review the four basic arithmetic operations, then the handling of the case of negative (signed) numbers.

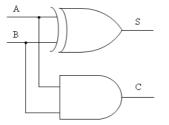

## **Binary Addition**

The algorithm of binary addition is similar to that of decimal numbers: aligning the numbers with the same radix, starting the addition with the pair of least significant digits. The **half adder** adds two single binary digits A and B. It has two outputs, sum (S) and carry (C). The rules for two-digit binary addition are the following:

| А |   | В |   | Sum | Carry                                |

|---|---|---|---|-----|--------------------------------------|

| 0 | + | 0 | = | 0   | 0                                    |

| 1 | + | 0 | = | 1   | 0                                    |

| 0 | + | 1 | = | 1   | 0                                    |

| 1 | + | 1 | = | 0   | 1 (to the next more significant bit) |

The half adder logic diagram is shown in Figure 2.1.

Figure 2.1 Half adder logic diagram

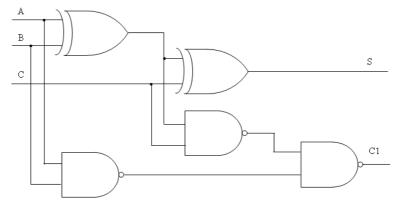

The rules of binary addition (without carries) are the same as the truths of the EXCLUSIVE OR (XOR) gate [9]. Circuit implementation requires 2 outputs; one to indicate the sum and another to indicate the carry. Two digits (bits) at the actual position and the carry from the previous position should be added. The process is then repeated. The **full adder** is a fundamental building block in many arithmetic circuits, which adds three one-bit binary numbers (C, A, B) having two one-bit binary output numbers, a sum (S) and a carry (C1).

| C A B       | S   | C1                                   |

|-------------|-----|--------------------------------------|

| 0 + 1 + 0 = | = 1 | 0                                    |

| 0 + 1 + 1 = | = 0 | 1 (to the next more significant bit) |

| 1 + 1 + 0 = | = 0 | 1 (to the next more significant bit) |

| 1 + 1 + 1 = | = 1 | 1 (to the next more significant bit) |

The full adder logic diagram is shown in Figure 2.2.

Figure 2.2 Full adder logic diagram

The following is an example of binary addition:

11 11 Carries 1001.011<sub>2</sub> Augend + 1100.111<sub>2</sub> Addend 10110.010<sub>2</sub> Sum

## **Binary Subtraction**

In many cases binary subtraction is done in a special way by binary addition. One simple building block called adder can be implemented and used for both binary addition and subtraction. Using the borrow method; the basic rules are summarized in the next:

| Borrow | А   | В   | Difference                                        |

|--------|-----|-----|---------------------------------------------------|

| 0      | 0 - | 0 = | 0                                                 |

| 0      | 1 - | 0 = | 1                                                 |

| 0      | 1 - | 1 = | 0                                                 |

| 0      | 0 - | 1 = | 1 and borrow 1 from the next more significant bit |

| 1      | 0 - | 0 = | 1 and borrow 1 from the next more significant bit |

| 1      | 0 - | 1 = | 0 and borrow 1 from the next more significant bit |

| 1      | 1 - | 0 = | 0                                                 |

| 1      | 1 - | 1 = | 1 and borrow 1 from the next more significant bit |

When a larger digit is to be subtracted from a smaller digit it is necessary to "borrow" from the next-higher-order digit position. The following example illustrates binary subtraction:

| 010                         | Modification of minuend resulting from borrowing |

|-----------------------------|--------------------------------------------------|

| <b>1</b> ′0 <b>1</b> ′0.11₂ | Minuend                                          |

| - 111.01 <sub>2</sub>       | Subtrahend                                       |

| 11. 102                     | Difference                                       |

|                             |                                                  |

## **Binary Multiplication**

The rules for two-digit binary multiplication are the next:

| А |   | В |   | Produc | t                           |

|---|---|---|---|--------|-----------------------------|

| 0 | Х | 0 | = | 0      |                             |

| 1 | Х | 0 | = | 0      |                             |

| 0 | Х | 1 | = | 0      |                             |

| 1 | Х | 1 | = | 1      | and no carry or borrow bits |

The rules of binary multiplication are the same as the truths of the AND gate [9]. In a very similar way to the decimal multiplication an array of partial products are formed and binary added. The following is an example of binary multiplication:

| $\begin{array}{c} 1 \ 1.1_2 \\ x \ 1 \ 0 \ 1_2 \end{array}$ | Multiplicand<br>Multiplier                 |

|-------------------------------------------------------------|--------------------------------------------|

|                                                             |                                            |

| 111                                                         | Array of partial product ( <b>1</b> x 111) |

| + 000                                                       | Array of partial product (00 x 111)        |

|                                                             |                                            |

| 0111                                                        |                                            |

| + 1 1 1                                                     | Array of partial product (100 x 111)       |

|                                                             |                                            |

| $1 \ 0 \ 0 \ 1.1_2$                                         | Product                                    |

## **Binary Division**

Binary division is the repeated process of subtraction, just as in decimal division [9]. A trial quotient digit is selected and multiplied by the divisor. The product is subtracted from the dividend to determine whether the trial quotient is correct. The principle of binary division is seen by the next example:

Divisor

$$11_2$$

) 10100000<sub>2</sub> Dividend

$-11$

$100$

$-11$

$100$

$-11$

$100$

$-00$

$100$

$-11$

$10$

$-00$

$100$

$-11$

$10$

$-00$

$100$

$-11$

$10$

$-00$

$100$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-00$

$100$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-00$

$100$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-11$

$10$

$-30$

$-11$

$10$

$-30$

$-11$

$10$

$-31$

$-10$

$-32$

Remainder

$37$

# 2.3 Signed Binary Numbers

The positive integers and the number zero can be represented as unsigned binary numbers using an n-bit word. When working with any kind of digital electronics in which numbers are being represented, it is important to distinguish both positive and negative binary numbers. The three representations of signed binary numbers will be discussed in the next. These approaches involve using one of the digits of the binary number to represent the sign of the number [10].

## **Sign-Magnitude Representation**

To mark the positive and negative quantities instead of using plus and minus sign we will use two additional symbols 0 and 1. In this approach the information's left bit (the most-significant bit, MSB) is the sign bit, where 0 denotes positive and 1 denotes negative value. The rest of the bits represent the number magnitude. This method is simple to implement, and is useful for point representation. The disadvantage floating of sign-magnitude representation is that the sign bit is independent of magnitude, and mathematical operations are more difficult. It is very important to not confuse this representation with unsigned numbers! Table 2.1 illustrates this concept, including all three representations of signed binary numbers using 4 bits. Here, the MSB bit (sign bit) is separated from the remaining 3 bits which denote the magnitude in the binary number system. It can be noted that 0 has two different representations, and can be both + 0 and - 0!

## **1's-Complement Representation**

The simplest of these methods is called 1's complement, which can be derived by just inverting all the bits in the number. Reversing the digits, by changing all the bits that are 1 to 0 and all the bits that are 0 to 1 is called complementing a number. The positive numbers 1's complement representation is the same as in the sign-magnitude approach and the 0 has again two different representations. In this approach the MSB bit also shows the sign of the number (all of the negative values begin with a 1, see Table 2.1).

## **2's-Complement Representation**

The 2's complement number representation is most commonly used for signed numbers on modern computers. An easier way to compute the 2's complement of a binary integer is to consider the 1's complement of the number plus 1. The 8 bit representations of the integer number -9 are:

| Signed-Magnitude representation: | 1 0001001 |

|----------------------------------|-----------|

| 1's complement:                  | 1 1110110 |

| 2's complement:                  | 1 1110110 |

| _                                | + 1       |

|                                  | 1 1110111 |

For further examples using 4 bits see Table 2.1.

| Signed decimal equivalent | Sign-magnitude representation | 1's complement representation | 2's complement representation |

|---------------------------|-------------------------------|-------------------------------|-------------------------------|

| +7                        | 0 111                         | 0 111                         | 0 111                         |

| +6                        | 0 110                         | 0 110                         | 0 110                         |

| +5                        | 0 101                         | 0 101                         | 0 101                         |

| +4                        | 0 100                         | 0 100                         | 0 100                         |

| +3                        | 0 011                         | 0 011                         | 0 011                         |

| +2                        | 0 010                         | 0 010                         | 0 010                         |

| +1                        | 0 001                         | 0 001                         | 0 001                         |

| 0                         | 0 000                         | 0 000                         | 0 000                         |

|                           | 1 000                         | 1 111                         |                               |

| -1                        | 1 001                         | 1 110                         | 1 111                         |

| -2                        | 1 010                         | 1 101                         | 1 110                         |

| -3                        | 1 011                         | 1 100                         | 1 101                         |

| -4                        | 1 100                         | 1 011                         | 1 100                         |

| -5                        | 1 101                         | 1 010                         | 1 011                         |

| -6                        | 1 110                         | 1 001                         | 1 010                         |

| -7                        | 1 111                         | 1 000                         | 1 001                         |

| -8                        |                               |                               | 1 000                         |

Table 2.1 Three representations of signed binary numbers using 4 bits

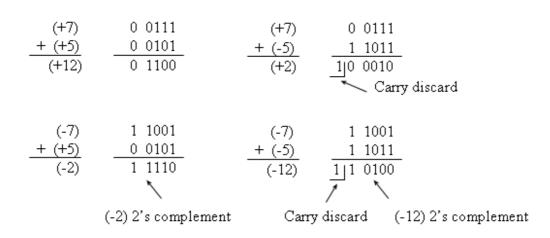

#### Addition with 2's Complement Representation

If the complement representation of signed numbers is used there is no need for both adder and subtractor unit in a computer.

Let's assume two n-bit signed numbers M and N represented in signed 2's complement format. The sum M + N can be obtained including their sign bits to get the correct sum. A carry out of the sign bit position is discarded. In the next, addition in the 2's complement representation examples are given (using 5 bits).

If the sum of two n-bit numbers results in an n + 1 number an overflow appears. The first step in the detection of such an error is the examination of the sign of the result. The overflow detection can be implemented using either hardware or software, and depends on the signed or unsigned number system used.

## 2.4 Binary Codes and Decimal Arithmetic

The binary number system, handling only two digit symbols, is the simplest system for a digital computer. From the user point of view it is easy to compute and operate with decimal numbers. A combination of binary and decimal approaches, keeping their advantages, result in a system in which the digits of the decimal system are coded by groups of binary digits. The basic concept is to convert decimal numbers to binary, to perform all arithmetic calculations in binary, and then convert the binary result back to decimal.

The best known scheme to code the decimal digits is the 8421 binary-codeddecimal (8421 BCD) scheme. In this **weighted code** 10 decimal digits are represented by at least 4 binary digits. In 8421 BCD code each bit is weighted by 8, 4, 2 and 1 respectively. For example the 8421 BCD representation of the decimal number 3581 is 0011 0101 1000 0001.

Beside 8421 BCD code other weighted codes have been used. These codes have fixed weights for different binary positions. It has been shown in [11] that exist 17 different set of weights possible for a positively weighted code: (3,3,3,1), (4,2,2,1), (4,3,1,1), (5,2,1,1), (4,3,2,1), (4,4,2,1), (5,2,2,1), (5,3,1,1), (5,3,2,1), (5,4,2,1), (6,2,2,1), (6,3,1,1), (6,3,2,1), (6,4,2,1), (7,3,2,1), (7,4,2,1), (8,4,2,1). It is also possible to have a weighted code in which some of the weights are negative, as in the 8, 4, -2, -1 code shown in Table 2.2.

| 8421<br>binary code | Excess-3<br>code                                                                    | 2-out-of-5<br>code                                                                      |

|---------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                     |                                                                                     |                                                                                         |

| 0000                | 0011                                                                                | 11000                                                                                   |

| 0001                | 0100                                                                                | 00011                                                                                   |

| 0010                | 0101                                                                                | 00101                                                                                   |

| 0011                | 0110                                                                                | 00110                                                                                   |

| 0100                | 0111                                                                                | 01001                                                                                   |

| 0101                | 1000                                                                                | 01010                                                                                   |

| 0110                | 1001                                                                                | 01100                                                                                   |

| 0111                | 1010                                                                                | 10001                                                                                   |

| 1000                | 1011                                                                                | 10010                                                                                   |

| 1001                | 1100                                                                                | 10100                                                                                   |

|                     | binary code<br>0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000 | binary codecode000000110001010000100101001101100100011101011000011010010111101010001011 |

Table 2.2 Binary codes for the decimal digits

This code has the useful property of being self-complementing: if a code word is formed by complementing each bit individually (changing 1's to 0's and vice versa), then this new code word represents the 9's complement of the digit to which the original code word corresponds [12].

The non-weighted codes don't have fixed weights for different binary positions. For example the excess-3 code is derived by adding  $0011_2 = 3_{10}$  to the 8421 BCD representation of each decimal digit. The 2-out-of-5 code shown in Table 2.2 has the property that each code word has exactly two 1's.

## **Decimal Addition Using 8421 BCD Code**

The 8421 BCD code is widely used and it is simplified as **BCD code**. Because of the popularity of this code in the next the addition operation is presented. Addition is performed by individually adding the corresponding digits of the decimal numbers expressed in 4-bit binary groups starting from right to left. [13]. If the result of any addition exceeds nine (1001) then the number six (0110) must be added to the sum to account for the six invalid BCD codes that are available with a 4-bit number.

Perform the following decimal additions (24 + 15) in BCD code.

When considering the two decimal numbers 26 and 37, it can be observed that the sum 6 + 7 = 13 > 9 and a correction is necessary to skip over the six illegal combinations (by adding a correction factor of  $6_{10} = 0110_2$ ). Thus, we have

|            | 26   | 0010 0110         |

|------------|------|-------------------|

|            | + 37 | <u>+0011 0111</u> |

|            |      | 0101 1101         |

| Correction |      | +0000 0110        |

| Sum        | 63   | 0110 0011         |

Consider the following addition: 28 + 59. When the sum of the LSB digits of the two numbers (8 + 9) is greater than 15 it is necessary to introduce a correction. In this approach a correct code group results but with an incorrect sum.

|            |      | carry      |

|------------|------|------------|

|            |      | ←          |

|            | 28   | 0010 1000  |

|            | + 59 | +0101 1001 |

|            |      | 1000 0001  |

| Correction |      | +0000 0110 |

| Sum        | 87   | 1000 0111  |

## 7-Segment Code

A very useful decimal code is the **7-segment code** which is able to show numeric info on seven-segment displays. The 7-segment display (see Figure 2.3) consist of 7 LEDs (light emitting diodes), each one controlled by an input where 1 means "on", 0 means "off". The decimal digit and the corresponding 7-segment code are shown in Table 2.3.

| Decimal Digit | 7-Segment Code |   |   |   |   |   |   |  |

|---------------|----------------|---|---|---|---|---|---|--|

|               | a              | b | с | d | е | f | g |  |

| 0             | 1              | 1 | 1 | 1 | 1 | 1 | 0 |  |

| 1             | 0              | 1 | 1 | 0 | 0 | 0 | 0 |  |

| 2             | 1              | 1 | 0 | 1 | 1 | 0 | 1 |  |

| 3             | 1              | 1 | 1 | 1 | 0 | 0 | 1 |  |

| 4             | 0              | 1 | 1 | 0 | 0 | 1 | 1 |  |

| 5             | 1              | 0 | 1 | 1 | 0 | 1 | 1 |  |

| 6             | 1              | 0 | 1 | 1 | 1 | 1 | 1 |  |

| 7             | 1              | 1 | 1 | 0 | 0 | 0 | 0 |  |

| 8             | 1              | 1 | 1 | 1 | 1 | 1 | 1 |  |

| 9             | 1              | 1 | 1 | 1 | 0 | 1 | 1 |  |

|               |                |   |   |   |   |   |   |  |

Figure 2.3 7-segment display

Table 2.3 Decimal digit and the corresponding7-segment code

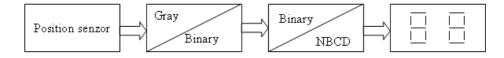

## **Gray Code**

The most useful **unit distance code** is the **Gray code** which is shown in Table 2.4. This unweighted code has such a sequence that any adjacent code words differ only in one bit (see subsection 1.4 Three - Variable Karnaugh Maps). The attractive feature of this code is the simplicity of the algorithm for translating from the binary number system into the Gray code. [12]

|         | Binary      | Gray     |

|---------|-------------|----------|

| Decimal | b2 b1 b0    | g2 g1 g0 |

| 0       | 0 0 0       | 0 0 0    |

| 1       | 0 0 1       | 0 0 1    |

| 2       | 0 1 0       | 0 1 1    |

| 3       | 0 1 1       | 0 1 0    |

| 4       | 1 0 0       | 1 1 0    |

| 5       | $1 \ 0 \ 1$ | 1 1 1    |

| 6       | 1 1 0       | 1 0 1    |

| 7       | 1 1 1       | 1 0 0    |

Table 2.4 The 3 bit Gray code

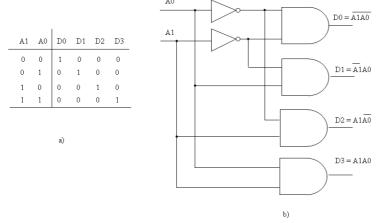

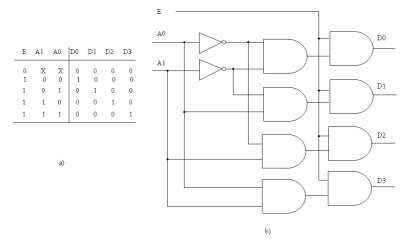

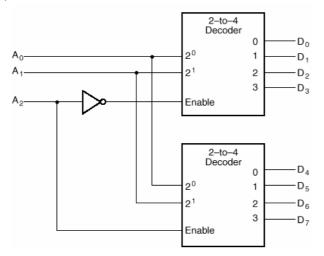

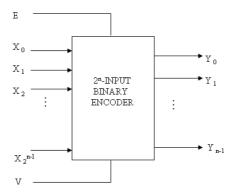

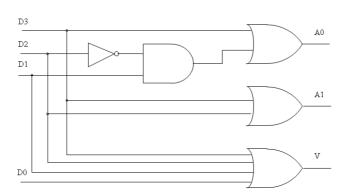

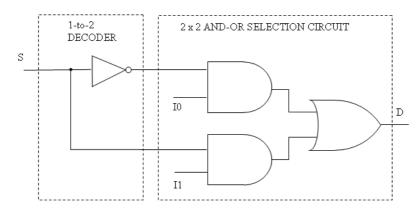

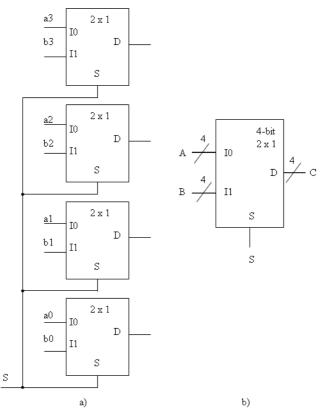

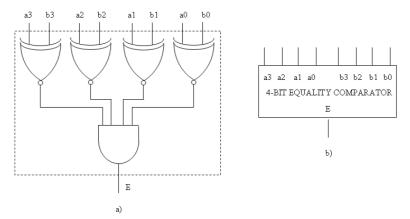

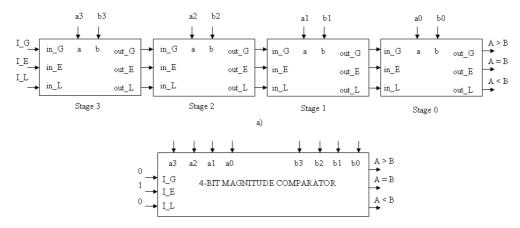

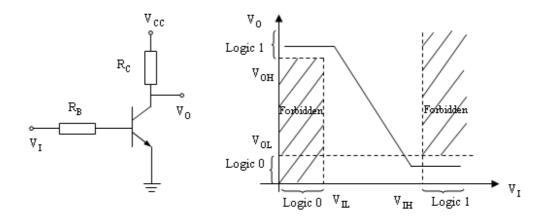

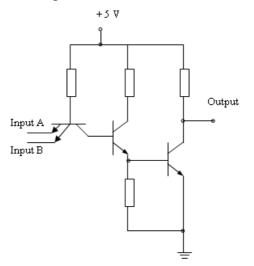

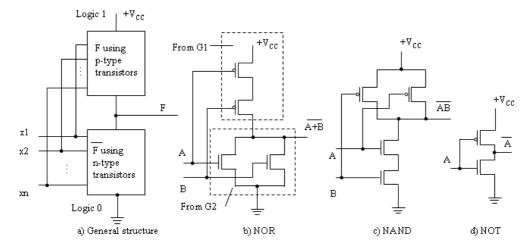

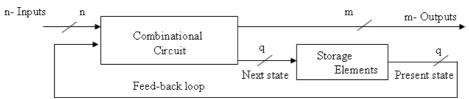

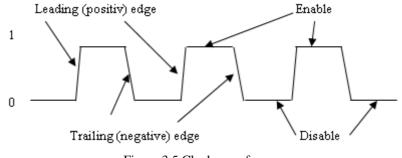

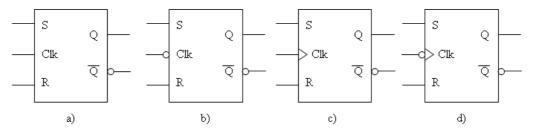

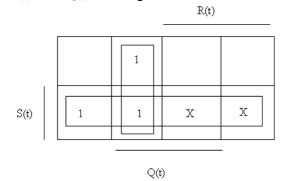

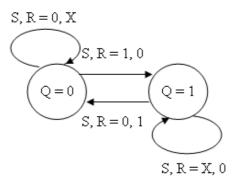

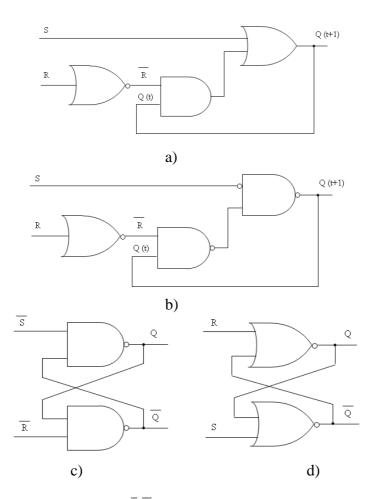

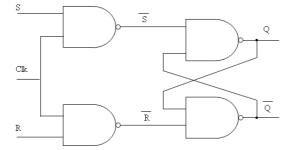

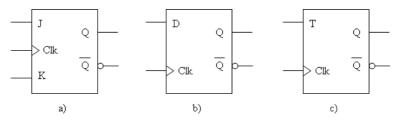

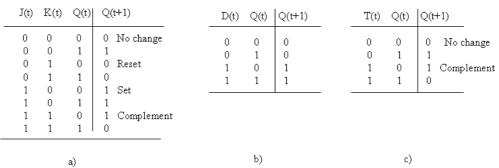

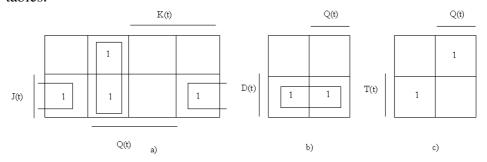

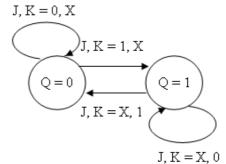

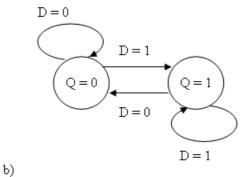

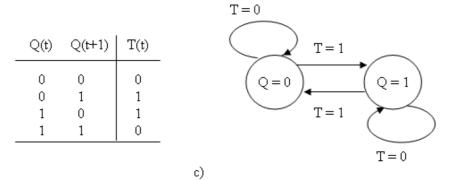

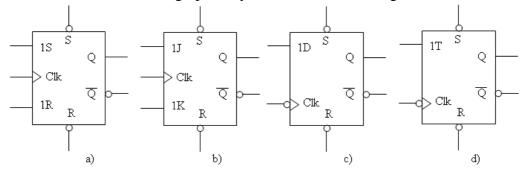

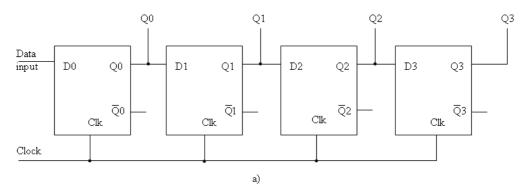

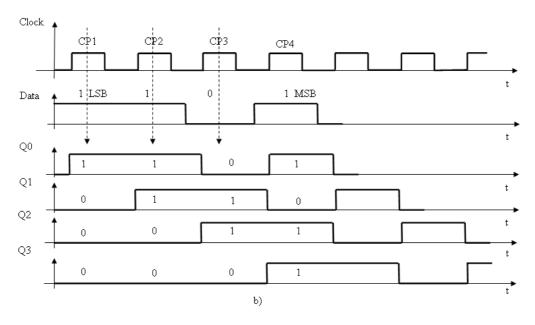

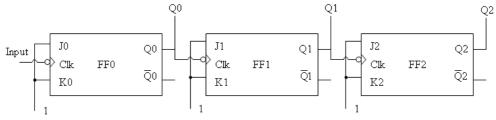

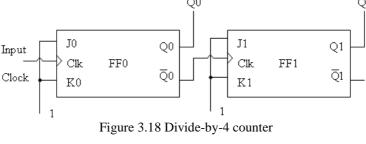

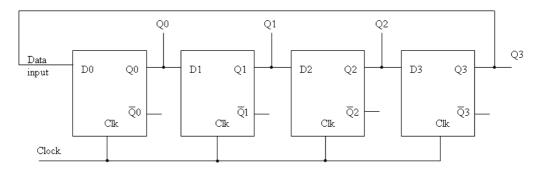

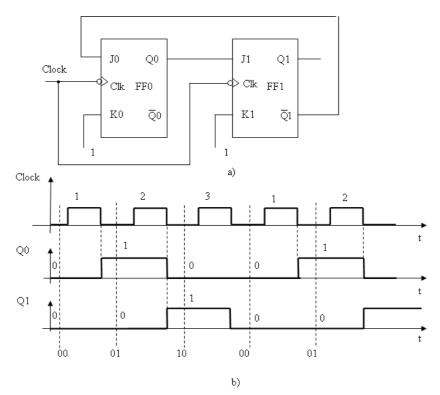

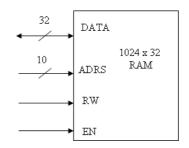

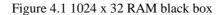

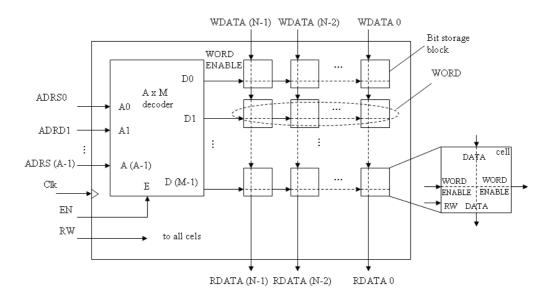

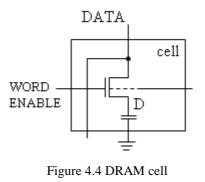

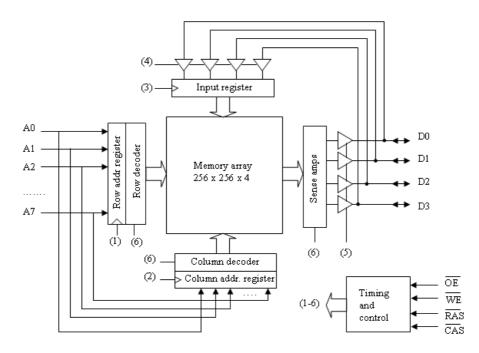

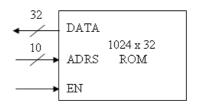

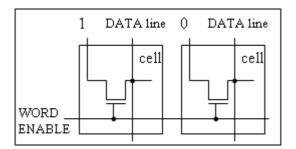

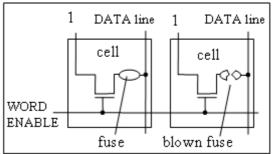

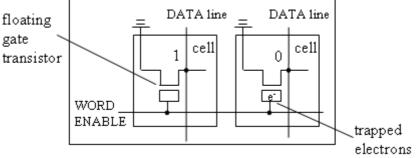

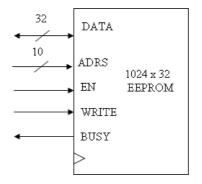

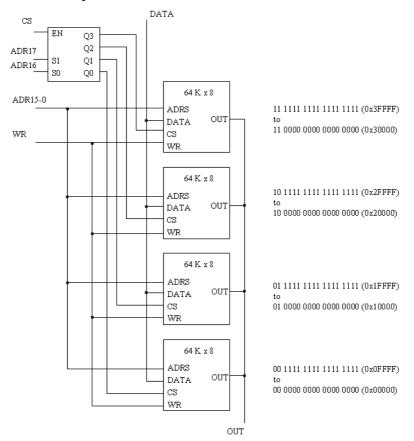

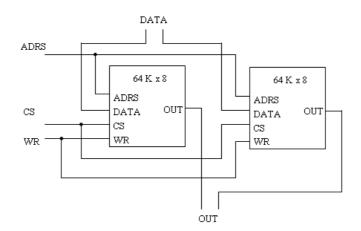

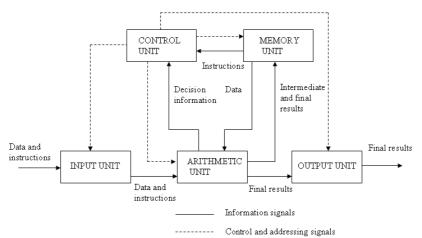

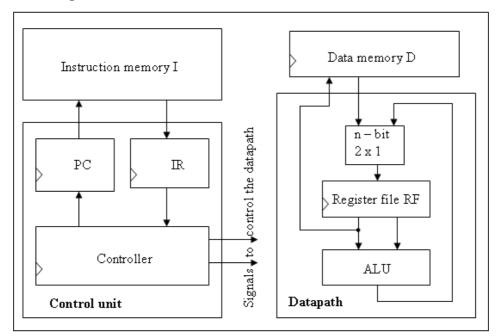

This algorithm is described by the expressions:  $g0 = b0 \oplus b1$   $g1 = b1 \oplus b2$ g2 = b2