# SYNTHESIS USING LOGIC GATES

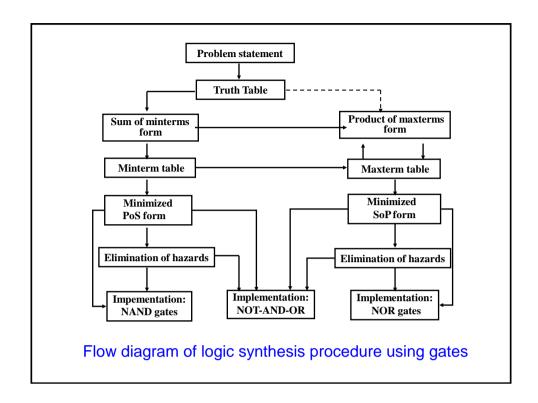

The traditional process of logic synthesis is based on the application of logic gates.

Its more modern variant makes use of programmable logic devices too.

However in many case it is more advantageous to use a logic synthesis procedure based on the application of logic functional blocks.

#### **IMPLEMENTING COMBINATIONAL LOGIC**

The different steps involved in the design of a combinational logic circuit are as follows:

- 1. Statement of the problem.

- 2. Identification of input and output variables.

- 3. Expressing the relationship between the input and output variables.

- 4. Construction of a truth table to meet input–output requirements.

- 5. Writing Boolean expressions for various output variables in terms of input variables.

- 6. Minimization of Boolean expressions.

- 7. Implementation of minimized Boolean expressions.

# **IMPLEMENTING COMBINATIONAL LOGIC**

These different steps are self-explanatory. One or two points, however, are worth mentioning here.

There are various simplification techniques available for minimizing Boolean expressions, which have been discussed in the previously. These include the use of theorems and identities, Karnaugh mapping, the Quine–McCluskey tabulation method and so on. Also, there are various possible minimized forms of Boolean expressions.

The following guidelines should be followed while choosing the preferred form for hardware implementation:

## IMPLEMENTING COMBINATIONAL LOGIC

1. The implementation should have the minimum number of gates, with the gates used having the minimum number of inputs.

- 2. There should be a minimum number of interconnections, and the propagation time should be the shortest.

- 3. Limitation on the driving capability of the gates should not be ignored.

It is difficult to generalize as to what constitutes an acceptable simplified Boolean expression. The importance of each of the above-mentioned aspects is governed by the nature of application.

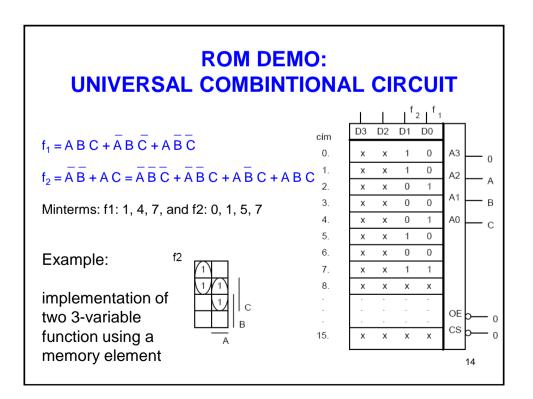

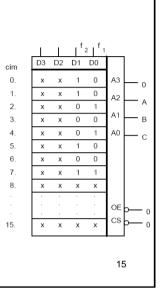

# ROM: UNIVERSAL COMBINTIONAL CIRCUIT

To implement the two 3-variable function a 8x2 bit ROM would be enough, but the smallest available on the market 16x4 bit .

A2, A1, A0 address – A, B, C variables D0, D1 outputs for f1, f2 functions.

Generation of truth table and programming: A3 address line connected to 0 (only the lower 8 words of the ROM is used, the remaining area is not relevant) D3, D2 – not relevant CS (*chip select*), OE (*output enable*) connected to active level, permanent enabling.

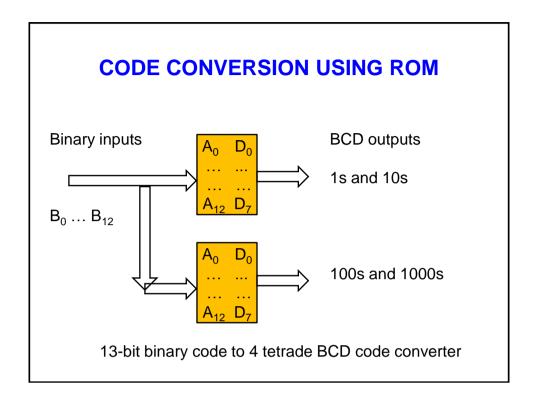

## **ROM APPLICATIONS:** CODE CONVERSIONS

One important application of ROMs in combinational logic is the code conversion.

n-bit code  $\rightarrow$  m-bit code  $\rightarrow$  necessary memory capacity: m x  $2^n.$

8-bit binary code  $\rightarrow$  8-bit Gray code: 256x8 ROM.

13-bit binary code  $\rightarrow$  4 tetrade BCD code: Two 8-kbyte kapacity EPROM, 1s, and 10s, and 100s and 1000s respectively, (13 bit: 0-8191).

# PROGRAMMABLE PERMANENT **MEMORIES (PROM)**

PROM Programmable Read Only Memory

Mask-programmed PROM: the manufacturer determines the contents of the ROM by appropriate layout of the interconnection metallization.

Field-programmable (burn-in) PROM (not erasable): the programming of the individual cells is accomplished by burning-out of the metal alloy or poly-silicon fuses belonging to the individual cells.

Original (virgin) state logic 1, burn-ot of the fuse programs-in logic 0.

Enabling technology: Si bipolar diodes/transistors.

23

## **REPROGRAMMABLE PROM:** EPROM AND EEPROM

EPROM (Erasable PROM) circuit technology: Si MOS FET.

Programming: injection of charges.

Erasing: Illumination with UV light, charges are released, information content is erased. After erasure the remaining state is either full 0 or full 1.

EEPROM Electrically Erasable PROM: can be erased electrically. Also MOS technology.

Representative parameters: programming/loading and erasing 10 – 50 msec. 24

Number of erasing processes: 10<sup>4</sup> - 10<sup>6</sup>.

# PROGRAMMABLE LOGIC DEVICES (PLD) FUNDAMENTALS

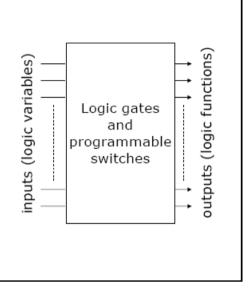

A PLD is a general purpose chip for implementing logic circuitry

Contains a collection of logic circuit elements that can be customized in different ways

Can be viewed as a black box containing logic gates and programmable switches that allow for different connections between the logic elements

Can implement whatever logic circuit is needed – subject to limitations of the device

#### PROGRAMMABLE LOGIC: ADDITIONAL ADVANTAGES

Many programmable logic devices are *field- programmable*, i.e., can be programmed outside of the manufacturing environment.

Most programmable logic devices are *erasable* and *reprogrammable*. Allows "updating" a device or correction of errors. Allows reuse the device for a different design - the ultimate in re-usability!

Programmable logic devices can be used to prototype design that will be implemented for sale in regular ICs.

Complete Intel Pentium designs were actually prototype with specialized systems based on large numbers of VLSI programmable devices!

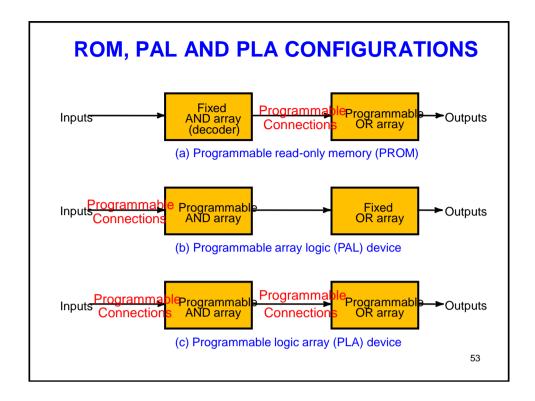

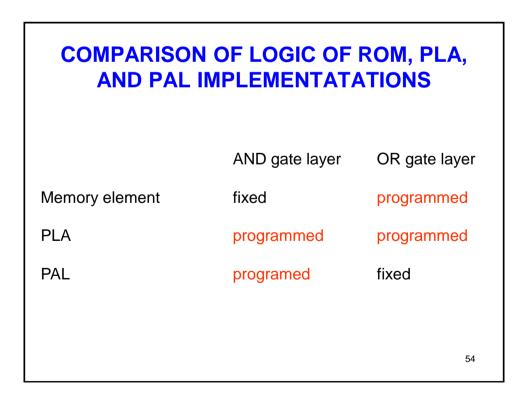

# **PROGRAMMABLE CONFIGURATIONS**

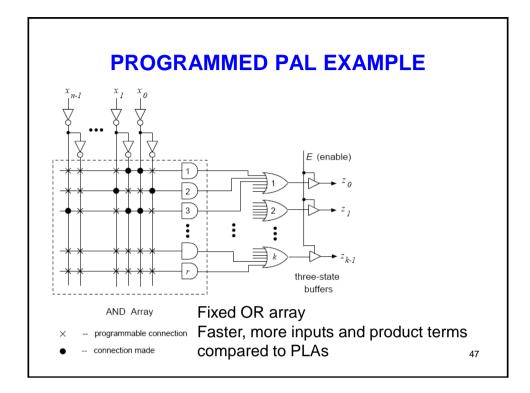

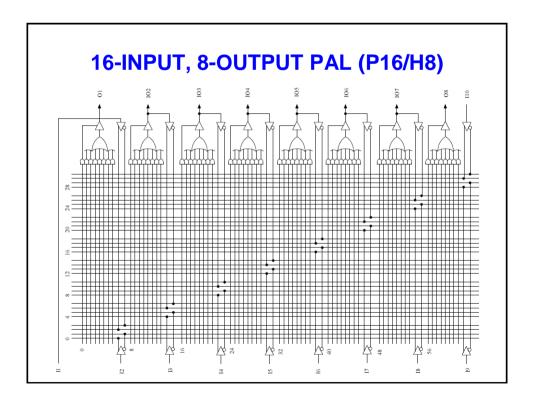

*Programmable Array Logic* (*PAL*)<sup>®</sup> - a programmable array of AND gates feeding a fixed array of OR gates.

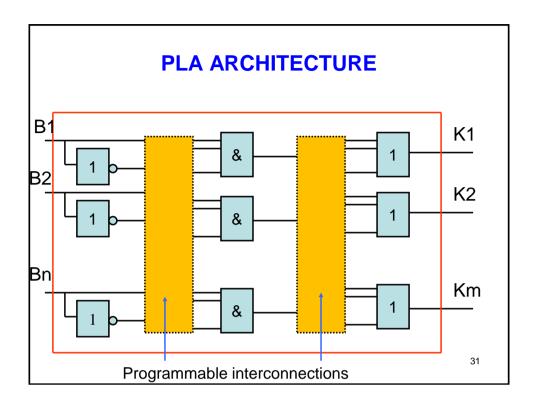

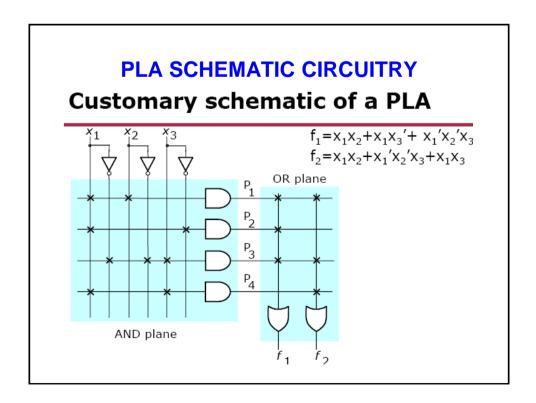

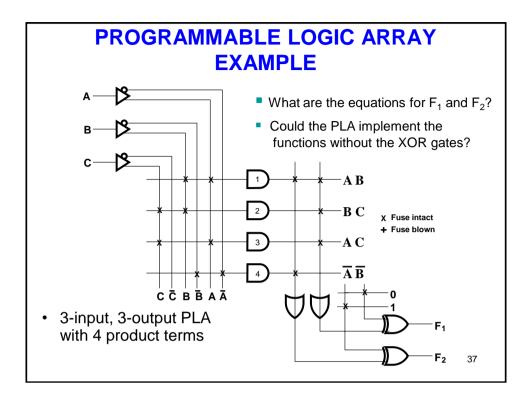

*Programmable Logic Array (PLA)* - a programmable array of AND gates feeding a programmable array of OR gates.

Complex Programmable Logic Device (CPLD) /Field-Programmable Gate Array (FPGA) - complex enough to be called "architectures".

# PROGRAMMABLE LOGIC DEVICES: PLD

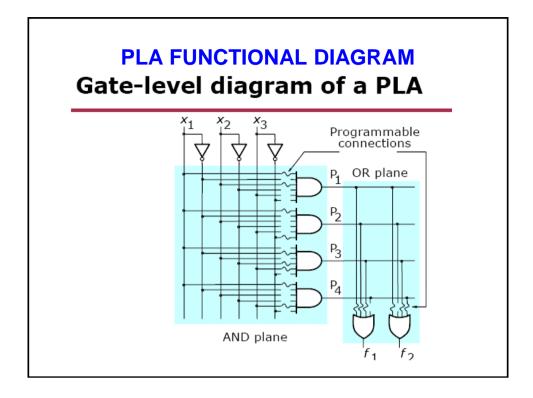

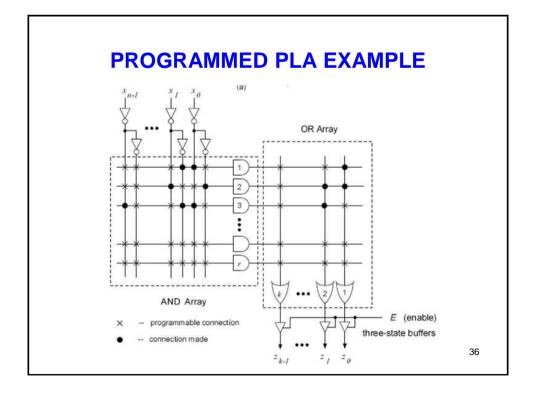

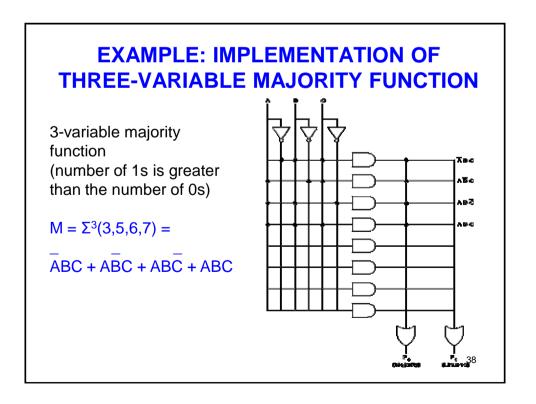

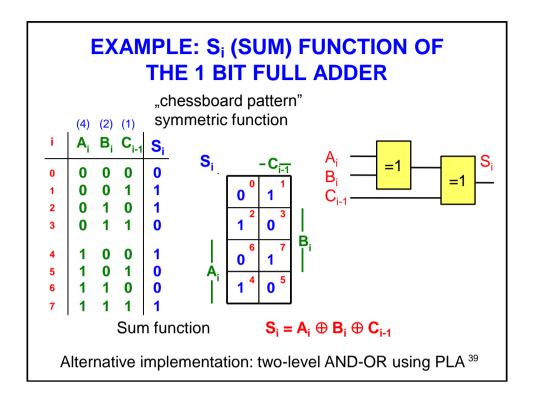

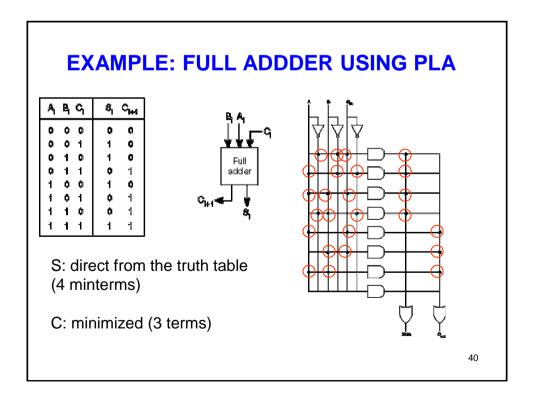

Programmable Logic Device (PLD) – one of the most common forms is the programmable logic matrix or Programmable Logic Array, PLA: certain number of AND and OR gates, and a number of inverters (to generate the negated values of the input variables).

The internal connections are realized on the basis of the conceptual logic diagram of the two-level multiple output combinational network.

In generating the conceptual logic diagamm the usual minimization and hazard elimination methods can be used.

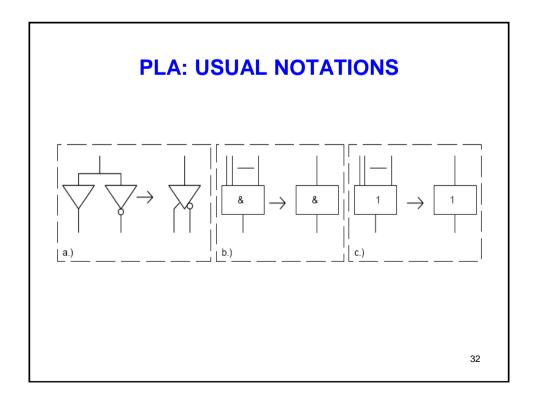

## PLA ELEMENTS: PROPERTIES AND USE

The technical characteristics of PLA elements determine whether one or more chips are necessary to implement a given combinational network:

- the number PLA inputs;

- the number of PLA outputs;

- the number of internal AND gates.

The number of inputs of internal AND gates usually agrees with the number of inputs of the whole PLA. The number of inputs of the internal OR gates usually corresponds to the number of internal AND gates. PLAs are also viable without incorporated input INVERTERs, the each input variable uses up two PLA inputs assisted by an external INVERTER.

<sup>35</sup>

# **PLA: HAZARDS**

In the case of a network implemented on a single PLA module the synthesis is based on the conceptual two-level logic diagram, and the hazard elimination might and should be performed using the standard procedures.

In the case of more complex networks consisting of several PLA elements further checks and analysis might be necessary.

49

# COMPARISON OF SOLUTIONS BASED ON MEMORY ELEMENTS AND ON PLA

Speed of operation:

Using PLA higher operational speeds can be achieved.

Reason: the PLA is essentially a two-level logic network, further on because of technological reasons a PLA is intrinsically faster then a memory element.

## COMPARISON OF SOLUTIONS BASED ON MEMORY ELEMENTS AND ON PLA

Hazards and hazard elimination:

When using PLA the hazard elimination should be performed during the synthesis applying the known procedures.

The behaviour of memory elements within the cycle is not defined ususally.

Solution: external control or synchronization.

51

## COMPARISON OF SOLUTIONS BASED ON MEMORY ELEMENTS AND ON PLA

Synthesis procedure:

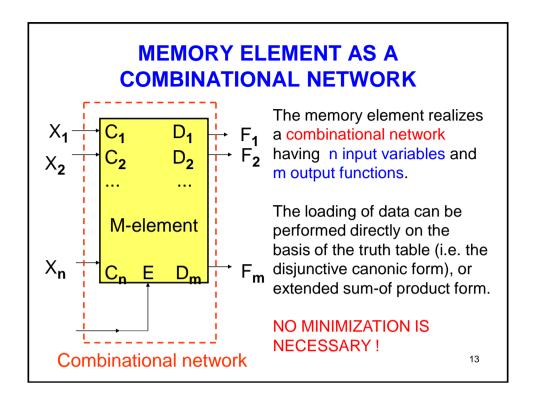

The synthesis procedure is simpler in the case of ROMs, because it is based directly on the truth table (extended sum-of product form).

In order to program a PLA it is necessary to establish the minimized hazard-free two level conceptual logic diagram.