### <section-header><section-header><section-header><text><text><text><text>

2nd (Autumn) term 2018/2019

### <section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item>

### **ARITHMETIC CIRCUITS**

- Excellent Examples of Combinational Logic Design

- Time vs. Space Trade-offs

- Doing things fast may require more logic and thus more space

- Example: carry lookahead logic

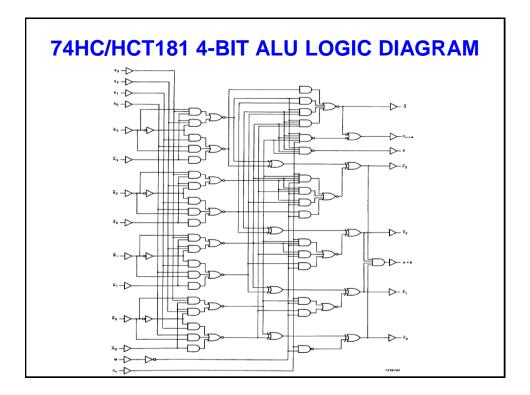

- Arithmetic and Logic Units

- General-purpose building blocks

- Critical components of processor datapaths

- Used within most computer instructions

### ARITHMETIC CIRCUITS: BASIC BUILDING BLOCKS

Below I will discuss those combinational logic building blocks that can be used to perform addition and subtraction operations on binary numbers. Addition and subtraction are the two most commonly used arithmetic operations, as the other two, namely multiplication and division, are respectively the processes of repeated addition and repeated subtraction.

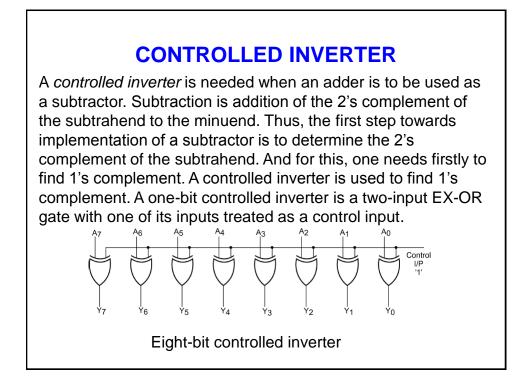

We will begin with the basic building blocks that form the basis of all hardware used to perform the aforesaid arithmetic operations on binary numbers. These include *half-adder*, *full adder*, *half-subtractor*, *full subtractor* and *controlled inverter*.

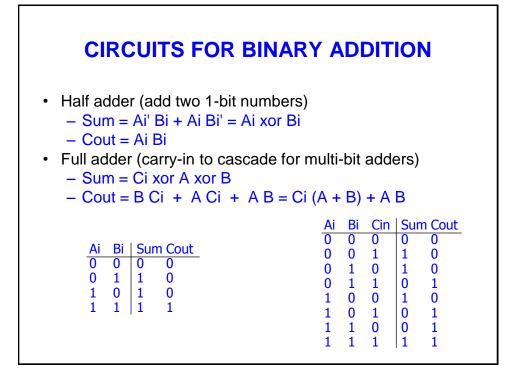

### HALF-ADDER AND FULL-ADDER

### Half-adder

This circuit needs 2 binary inputs and 2 binary outputs. The input variables designate the augend and addend bits: the output variables produce the sum and carry.

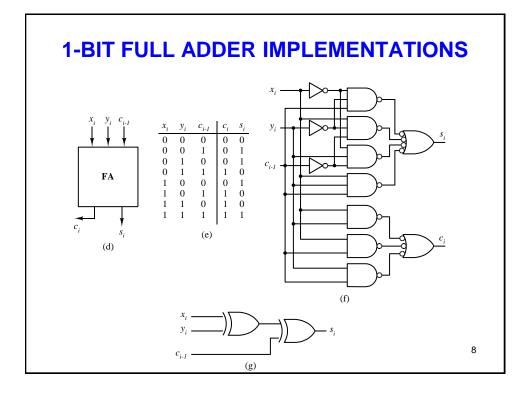

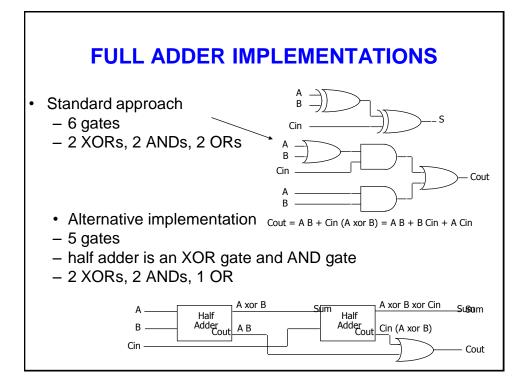

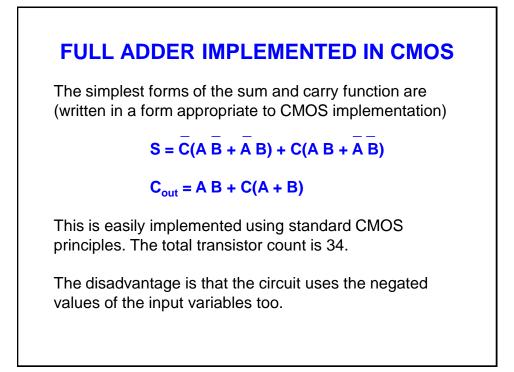

### **Full-adder**

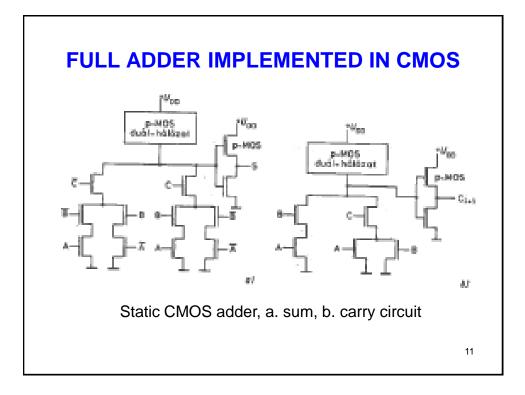

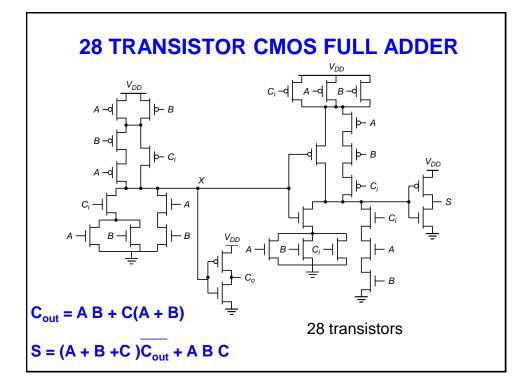

Is a combinational circuit that forms the arithmetic sum of 3 bits. Consists of 3 inputs and 2 outputs. When all input bits are 0, the output is 0. The output S equal to 1 when only one input is equal to 1 or when all 3 inputs are equal to 1.

The C output has a carry of 1 if 2 or 3 inputs are equal to 1.

### <text><equation-block><equation-block><text><text><text><text>

## <text><equation-block><equation-block><text><text><text><text><text>

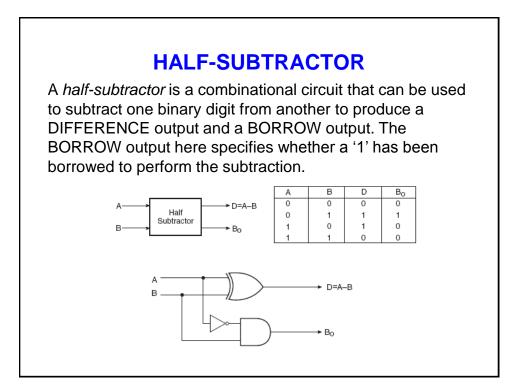

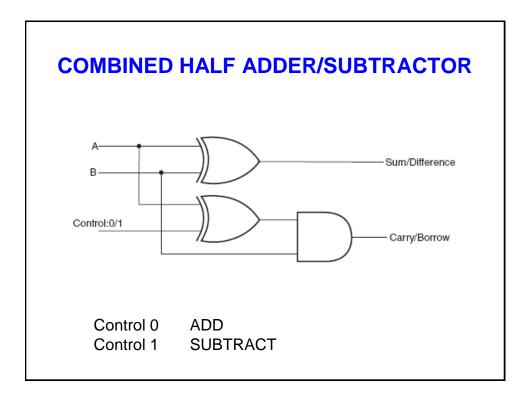

### HALF- AND FULL SUBTRACTOR

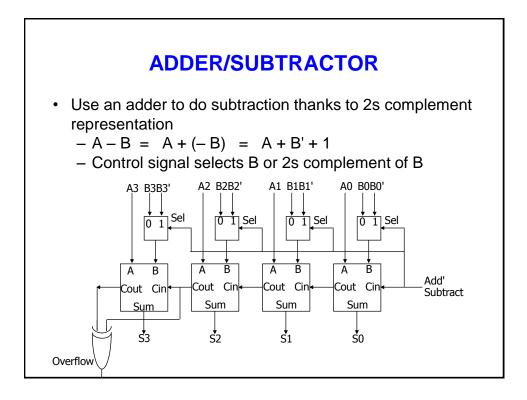

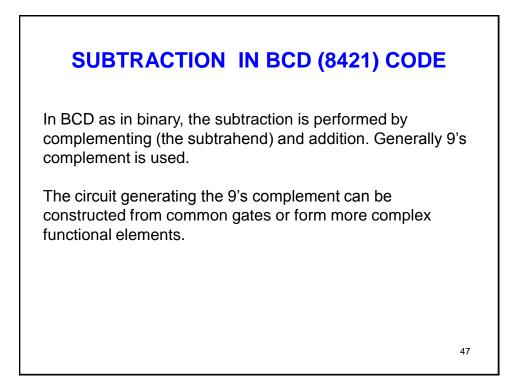

The subtraction of two given binary numbers canbe carried out by adding 2's complement of the subtrahend to the minuend. This allows us to do a subtraction operation with adder circuits.

However, we will also briefly look at the counterparts of half-adder and full adder circuits in the *half-subtractor* and *full subtractor* for direct implementation of subtraction operations using logic gates.

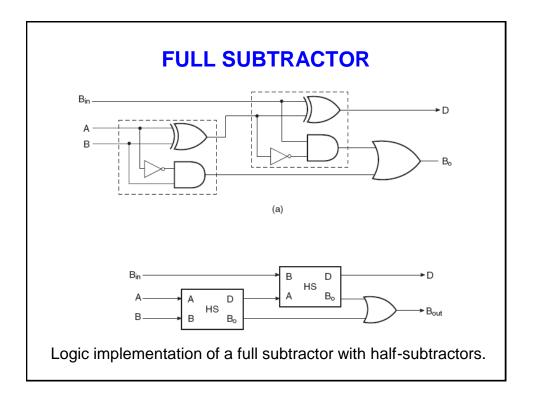

### **FULL SUBTRACTOR**

A *full subtractor* performs subtraction operation on two bits, a *minuend* and a *subtrahend*, and also takes into consideration whether a '1' has already been borrowed by the previous adjacent lower minuend bit or not. As a result, there are three bits to be handled at the input of a *full subtractor*, namely the two bits to be subtracted and a borrow bit designated as Bin . There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo. The BORROW output bit tells whether the minuend bit needs to borrow a '1' from the next possible higher minuend bit.

| FULL SUBTRACTOR                                                                    |                |                   |                    |                   |                                 |  |

|------------------------------------------------------------------------------------|----------------|-------------------|--------------------|-------------------|---------------------------------|--|

| $A \longrightarrow Full \\ B \longrightarrow Subtractor \\ Bin \longrightarrow Bo$ | Minuend<br>(A) | Subtrahend<br>(B) | Borrow<br>In (Bin) | Difference<br>(D) | Borrow<br>Out (B <sub>0</sub> ) |  |

|                                                                                    | 0              | 0                 | 0                  | 0                 | 0                               |  |

|                                                                                    | 0              | 0                 | 1                  |                   | 1                               |  |

|                                                                                    | 0              | 1                 | 0                  | 1                 | 1                               |  |

|                                                                                    | 0              | 1                 | 1                  | 0                 | 1                               |  |

|                                                                                    | 1              | 0                 | 0                  | 1                 | 0                               |  |

|                                                                                    | 1              | 0                 | 1                  | 0                 | 0                               |  |

|                                                                                    | 1              | 1                 | 0                  | 0                 | 0                               |  |

|                                                                                    | 1              | 1                 | 1                  | 1                 | 1                               |  |

| Truth table of a full subtractor                                                   |                |                   |                    |                   |                                 |  |

### **RIPPLE CARRY ADDER**

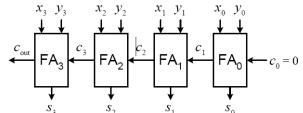

The full adder is for adding two operands that are only one bit wide. To add two operands that are, say four bits wide, we connect four full adders together in series. The resulting circuit is called a ripple carry adder for adding two 4-bit operands.

The ripple-carry adder is slow because the carry-in tor each full adder is dependent on the carry-out signal from the previous FA. So before  $FA_i$  can output valid data, it must wait for  $FA_{i-1}$  to have valid data.

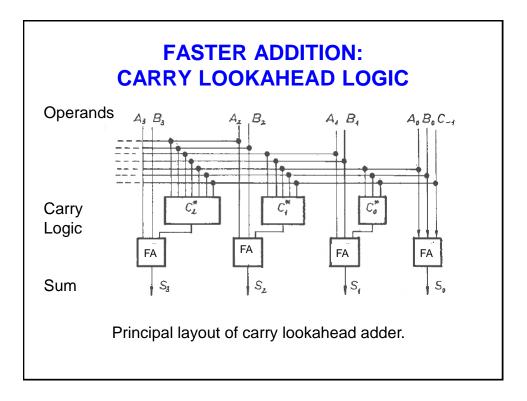

### **CARRY-LOOKAHEAD ADDER**

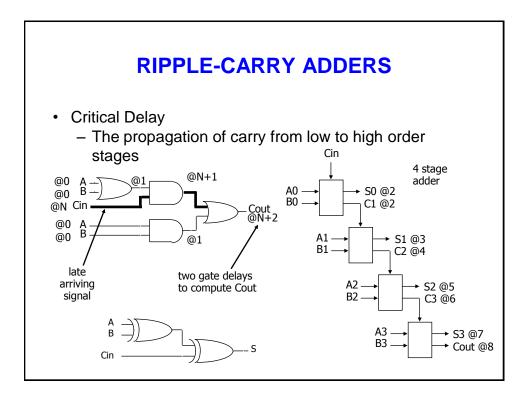

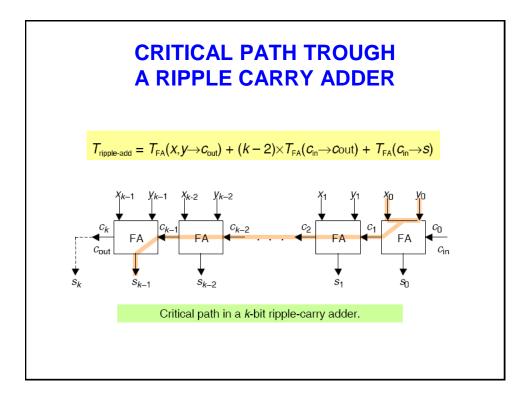

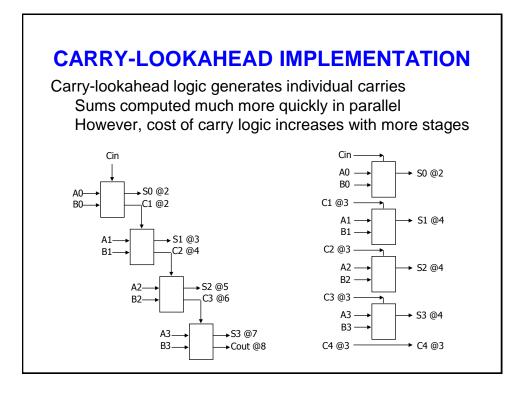

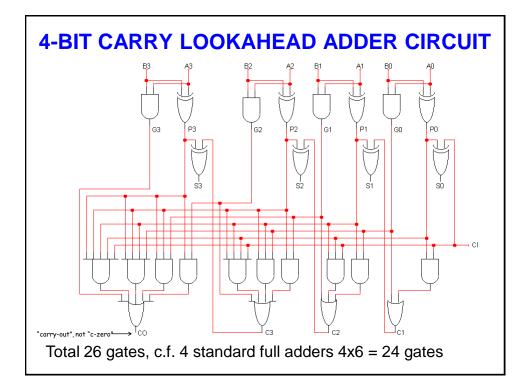

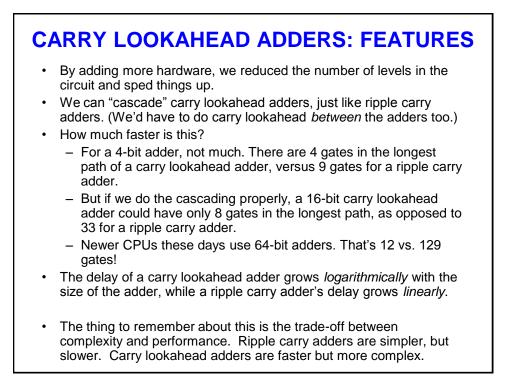

The layout of a ripple carry adder is simple, which allows for fast design time, however, the ripple carry adder is relatively slow, since each full adder must wait for the carry bit from the previous full adder.

From  $C_{in}$  to  $C_{out}$  2 gates should be passed through. Ergo a 32-bit adder requires 31 carry computations and the final sum calculation for a total of 31x2 + 1 = 63 gate delays.

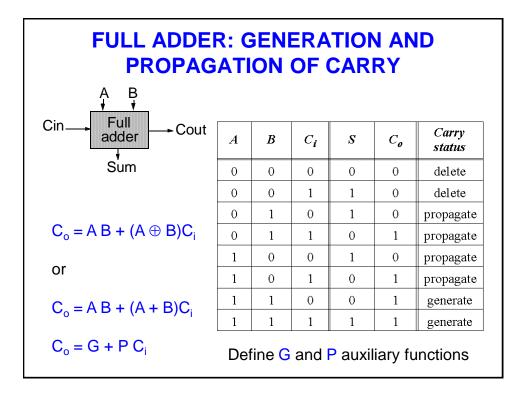

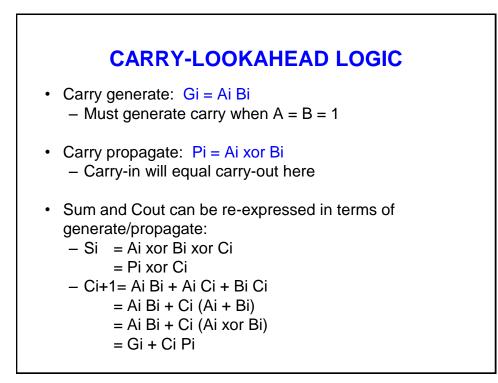

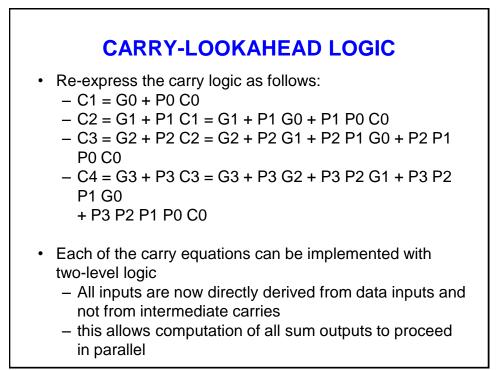

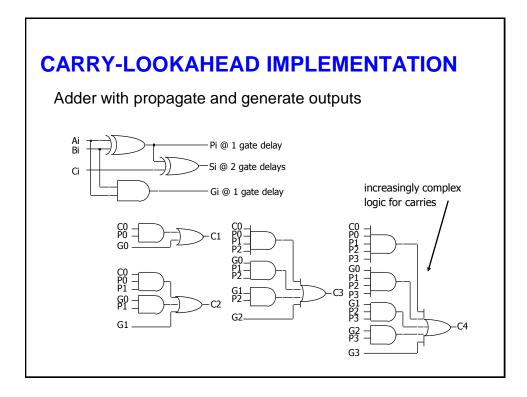

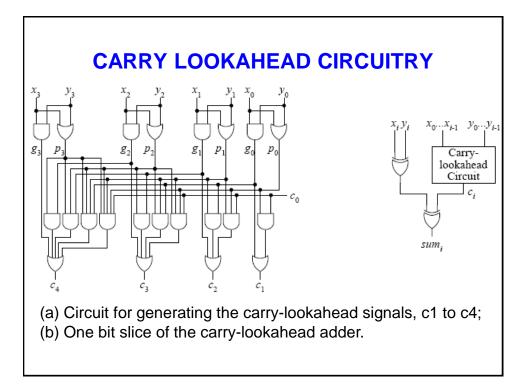

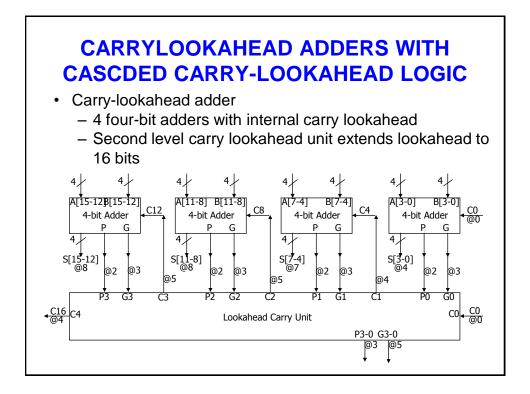

In the *carry-lookahead* adder, each bit slice eliminates this dependency on the previous carry-out signal and instead uses the values of the two input operands, directly to deduce the needed signals. This is possible from the following observations regarding the carry-out signal.

# <text><text><text>

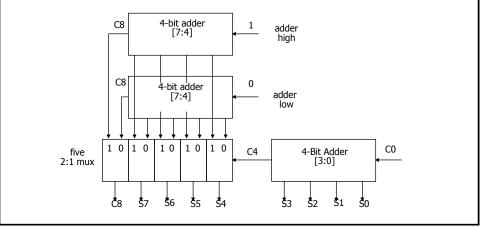

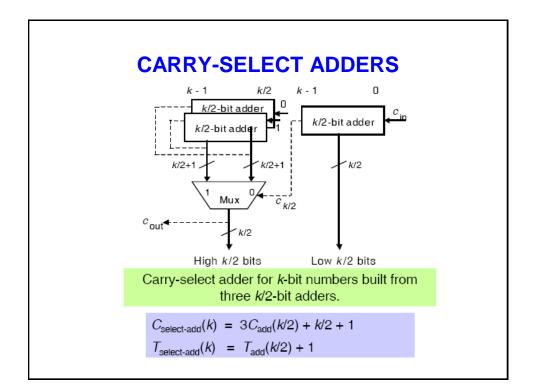

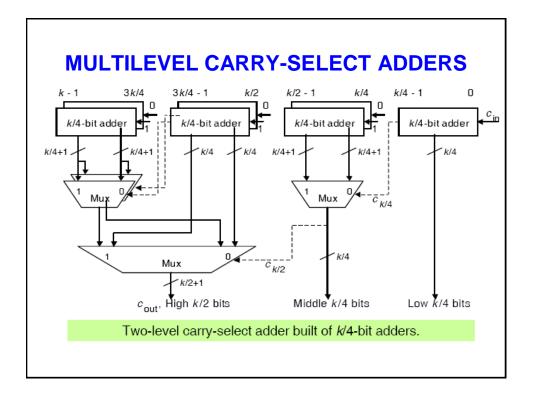

### **CARRY-SELECT ADDER**

Redundant hardware to make carry calculation go faster Compute two high-order sums in parallel while waiting for carry-in One assuming carry-in is 0 and another assuming carry-in is 1 Select correct result once carry-in is finally computed

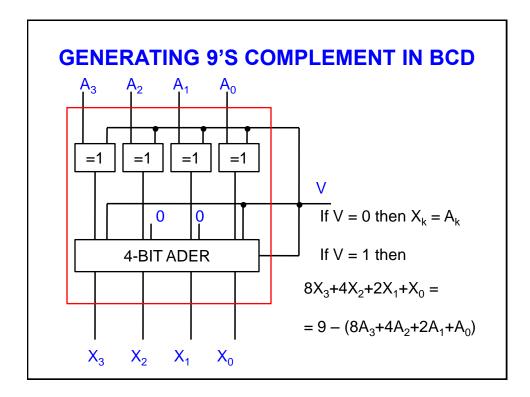

### **ARITHMETICAL OPERATIONS IN BCD**

Many digital systems (processors, computers) can perform the arithmetical operations or a part of them directly on BCD numbers.

E.g. the microprocessors can perform BCD addition, several of them subtraction too. Certain special processors can perform BCD multiplication and division too.

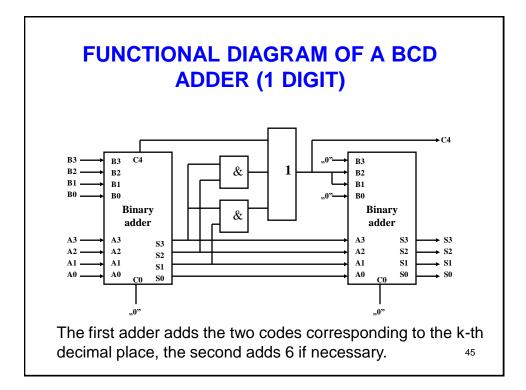

The BCD addition is reduced to binary addition. The tetrades of the operands are added as binary numbers, and if necessary (illegal codewords or decimal carry is generated during the addition), a systematic correction is performed.

### **BCD ADDITION**

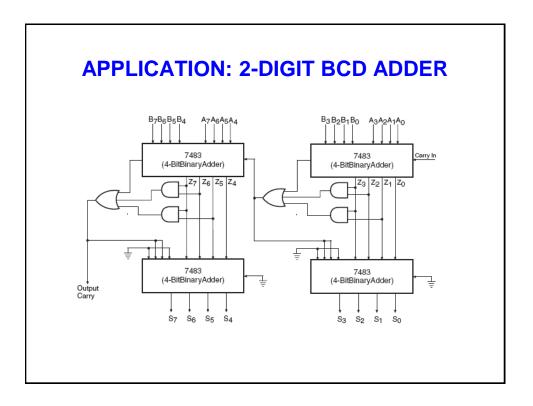

A BCD adder is used to perform the addition of BCD numbers. A BCD digit can have any of the ten possible four-bit binary representations, that is, 0000, 0001, , 1001, the equivalent of decimal numbers 0, 1, ..., 9. When we set out to add two BCD digits and we assume that

there is an input carry too, the highest binary number that we can get is the equivalent of decimal number 19 (9+9+1). This binary number is going to be  $(10011)_{bin}$ . On the other hand, if we do BCD addition, we would expect the answer to be  $(0001\ 1001)_{BCD}$ . And if we restrict the output bits to the minimum required, the answer in BCD would be  $(1\ 1001)_{BCD}$ .

### **ADDITION IN NORMAL BCD (8421) CODE**

If the sum of two tetrades is not larger than 9, the result is valid, no correction is necessary.

If the sum of two tetrades is larger than 9, (decimal carry and illegal codeword or pseudotetrade is generated) the result is valid only in binary system and not in BCD. The necessary correction is to add decimal 6 or i.e. binary 0110 to the actual tetrade.

The correction should be performed beginning form the least significant tetrade and going upwards step-by-step.

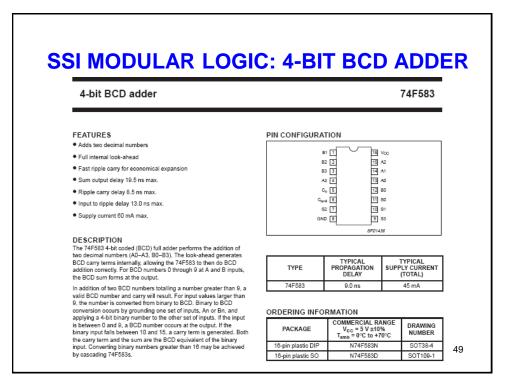

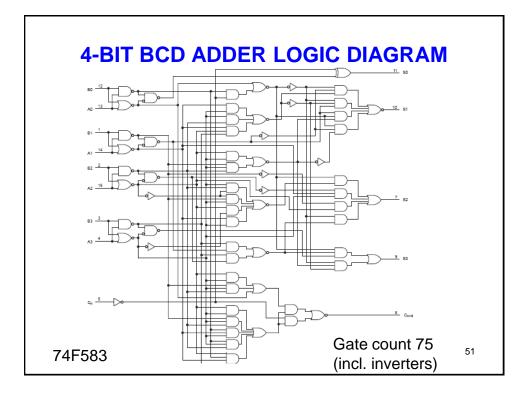

### **SSI MODULAR LOGIC: 4-BIT BCD ADDER**

The 74F583 4-bit coded (BCD) full adder performs the addition of two decimal numbers (A0–A3, B0–B3). The look-ahead generates BCD carry terms internally, allowing the 74F583 to do BCD addition correctly.

For BCD numbers 0 through 9 at A and B inputs, the BCD sum forms at the output.

In addition of two BCD numbers totalling a number greater than 9, a valid BCD number and carry will result.

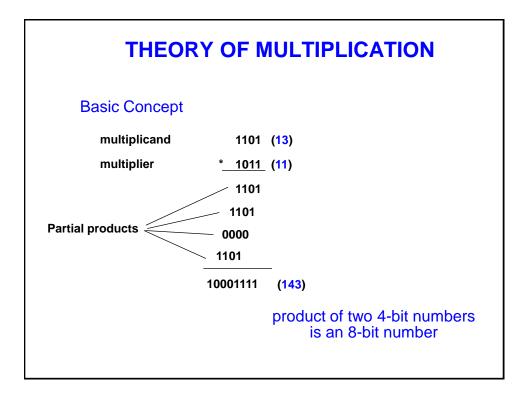

### **MULTIPLIERS**

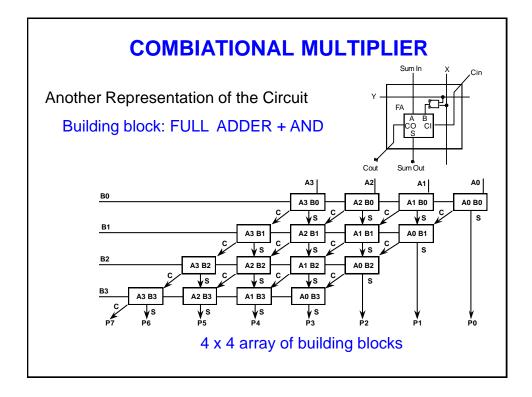

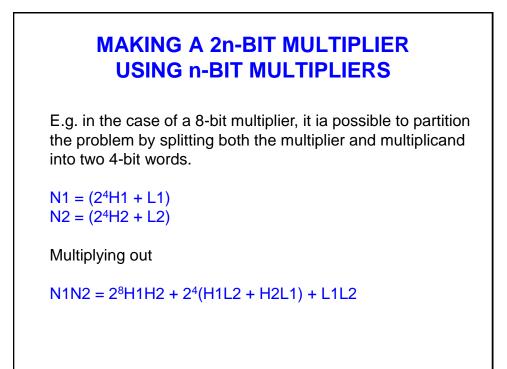

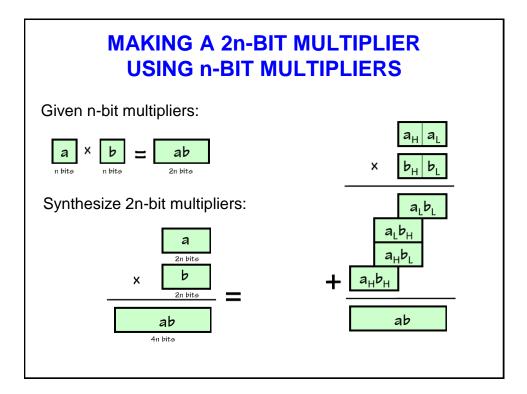

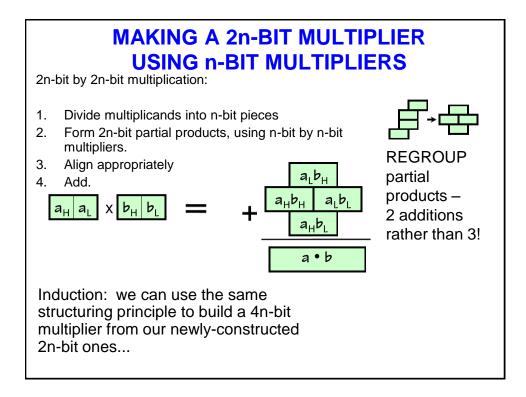

A binary multiplier is an electronic circuit used in digital electronics, such as a computer, to multiply two binary numbers.

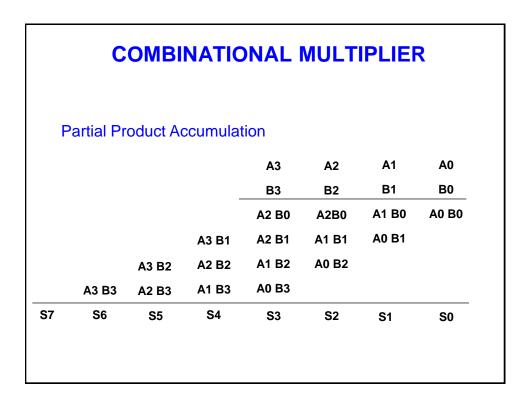

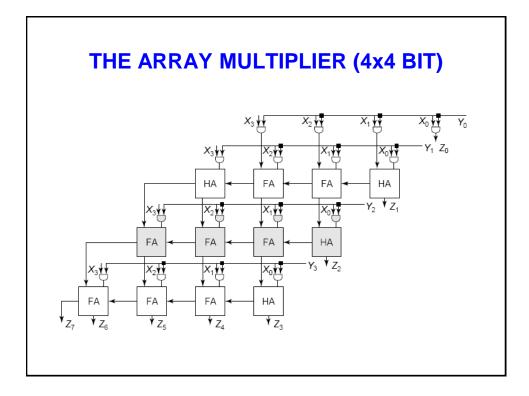

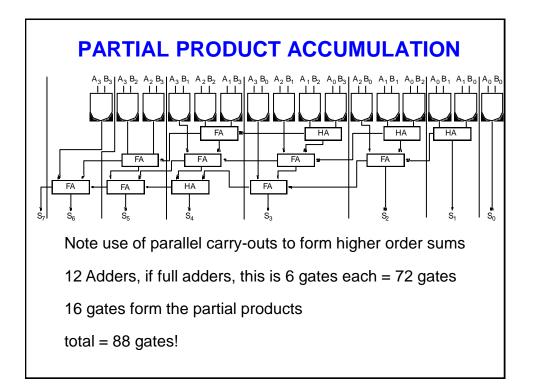

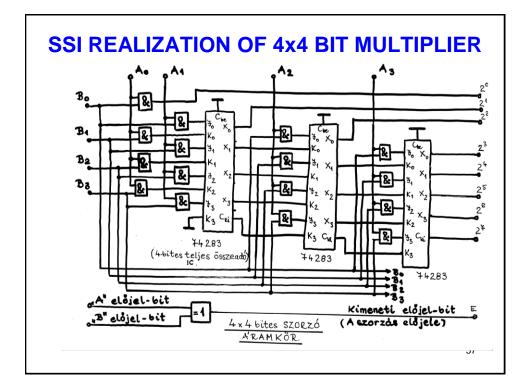

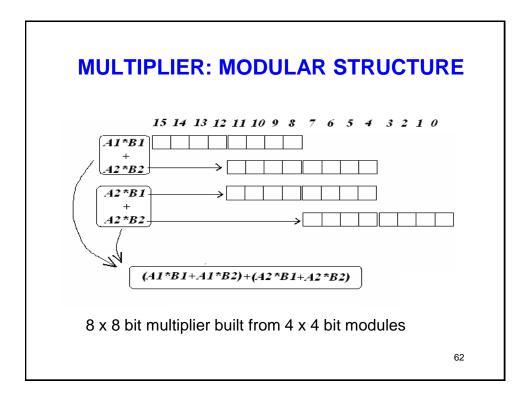

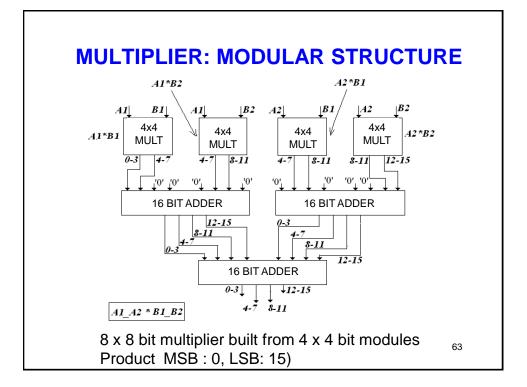

A variety of computer arithmetic techniques can be used to implement a digital multiplier. Most techniques involve computing a set of partial products, and then summing the partial products together. This process is similar to the method taught to primary school children for conducting long multiplication on base-10 integers, but has been modified here for application to a base-2 (binary) numeral system.

The first stage of most multipliers involves generating the partial products which is nothing but an array of AND gates. An n-bit by n-nit multiplier requires n<sup>2</sup> AND gates for partial product generation.

The partial products are then added to give the final results.

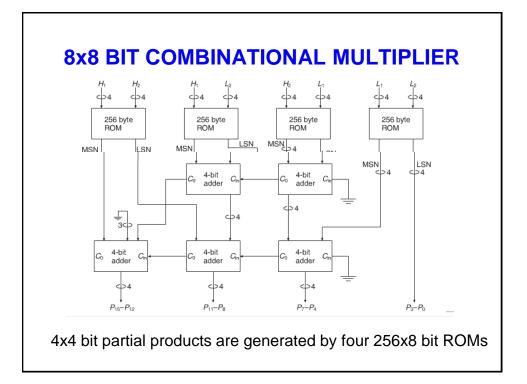

### **ROM IMPLEMENTED MULTIPLIER**

Binary multiplication can be achieved by using a ROM as a "look-up table". E.g., multiplication of two 4-bit numbers requires a ROM having eight address lines, four of them X4XRX2X1 being allocated to the multiplier, and the remaining four, Y4Y3Y2Y1 to the multiplicand. Since the multiplication of two 4-bit numbers can result in a double-length product, the ROM should have eight output lines, and a room with capacity of 256 bytes is required.

For two 8-bit numbers  $2^{16} = 65336$  memory locations and 16 output lines for the double-length products are required. This requires a ROM of 128 kbytes. For 16-bit multiplication the required ROM capacity is formidable (16 Gbytes!).

### **MULTIPLICATION: NEGATIVE NUMBERS**

The basic school method of multiplication handles the sign with a separate rule ("+ with + yields +", "+ with - yields -", etc.). Modern computers embed the sign of the number in the number itself, usually in the two's complement representation. That forces the multiplication process to be adapted to handle two's complement numbers, and that complicates the process a bit more. Similarly, processors that use one's complement sign-and-magnitude, IEEE-754 or other binary representations require specific adjustments to the multiplication process.

### **MULTIPLICATION: SPEEDING IT UP**

Older multiplier architectures employed a shifter and accumulator to sum each partial product, often one partial product per cycle, trading off speed for die area.

Modern multiplier architectures use the *Baugh-Wooley algorithm*, *Wallace tree* or *Dadda* to add the partial products together in a single cycle. The performance of the *Wallace tree* implementation is sometimes improved by modified *Booth encoding* one of the two multiplicands, which reduces the number of partial products that must be summed.

### **BOOTH ENCODING MULTIPLICATION**

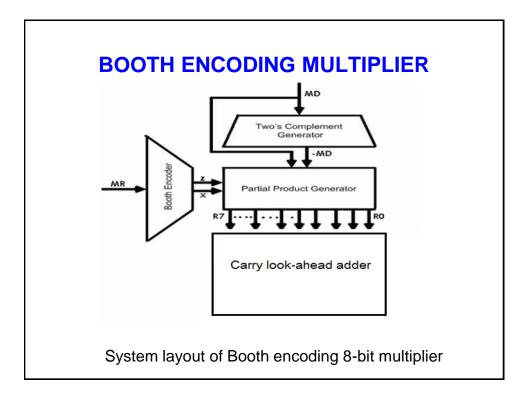

The multiplier takes in two 8-bits operands: the multiplier(MR) and the multiplicand (MD), then produces 16-bit multiplication result of the two as its output.

The architecture comprises four parts: Complement Generator, Booth Encoder, Partial Product and Carry Look-ahead Adder.

### **BOOTH ENCODING DEMO**

$X \times 00111110 = X \times (2^5 + 2^4 + 2^3 + 2^2 + 2^1) = X \times 62$

The number of partial product and the number of operations can be reduced to two by rewriting the equation as

$X \times 00111110 = X \times (2^{6} - 2^{1}) = X \times (64 - 2) = X \times 62$

When Booth encounters the first digit of a block of ones (0 1), it follows this scheme. When Booth encounters the end of the block (1 0), it follows a subtraction.

### **MULTIPLIERS: COMPLEXITY**

Transistor count for generic multiplier circuits is based on static CMOS implementation

| 8-bit                  | 3000  |  |  |  |  |

|------------------------|-------|--|--|--|--|

| 16-bit                 | 9000  |  |  |  |  |

| 32-bit                 | 21000 |  |  |  |  |

| i.e. in the LSI range. |       |  |  |  |  |

### **REVISION QUESTIONS**

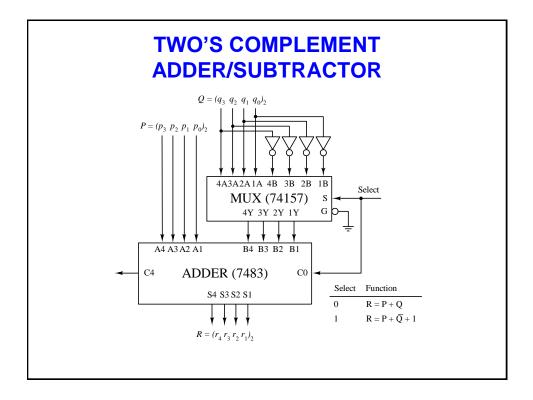

1. Present the layout of the two's complement adder/substractor and explain its operation.

2. Describe the operation of the carry lookahead adder.

3. Describe the operation of the carry-select adder.

4. Present the layout of a (one digit) BCD adder and explain its operation.

5. Describe the layout and operation of the combinational multiplier.

### **PROBLEMS AND EXERCISES**

1. Implement the 2-bit adder function (i.e., 2-bit binary number *AB* plus 2-bit binary number *CD* yields 3-bit result *XYZ*) using three 8:1 multiplexers. Show your truth table and how you derived the inputs to the multiplexers.

2. Construct a circuit which multiplies a 4-bit binary number (X3 X2 X1 X0) by six. Use a 4-bit adder (functional block), and a minimum number of other gates.

3. Design an eight-bit adder–subtractor circuit using four-bit binary adders, type number 7483, and quad two-input XOR gates, type number 7486. Assume that pin connection diagrams of these ICs are available to you. Give short description of your design and its operation.

### PROBLEMS AND EXERCISES

4. Design a BCD adder circuit capable of adding BCD equivalents of two-digit decimal numbers. Indicate the IC type numbers used if the design has to be TTL logic family compatible.

5. Using representation on 8 bits perform in 2's complement the following operations:

25+30=? 25-30=? 30-25=?