### **STATE MACHINE SYNTHESIS**

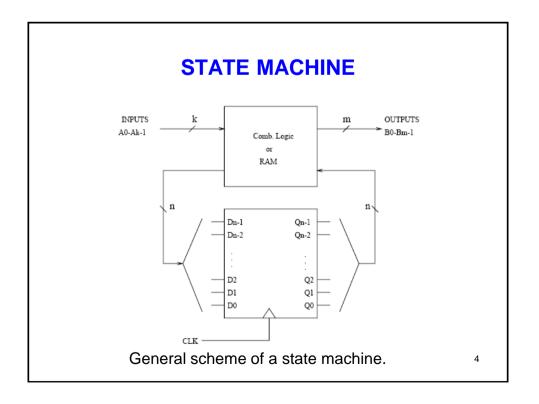

The strategy for applying this scheme to a given problem consists of the following:

1. Identify the number of required states, m. The number of bits of memory (e.g. number of flip-flops) required to specify the m states is at minimum  $n = log_2(m)$ .

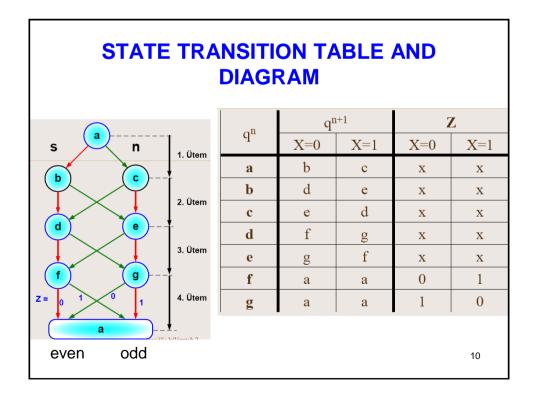

2. Make a state diagram which shows all states, inputs, and outputs.

3. Make a truth table for the logic section. The table will have n + k inputs and n + m outputs.

4. Implement the truth table using combinational logic techniques.

5

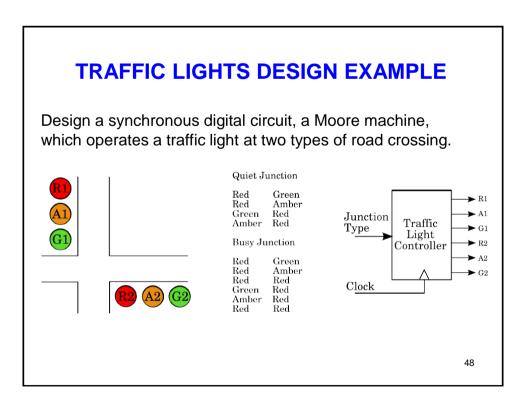

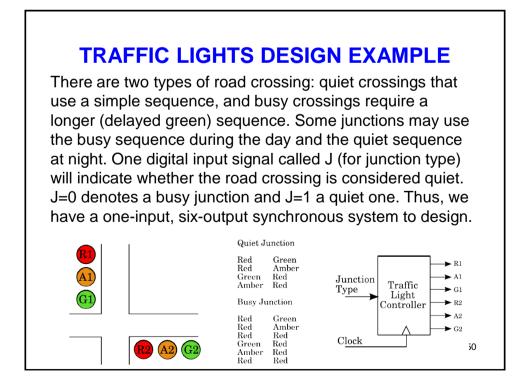

### SYNTHESIS OF SEQUENTIAL CIRCUIT: A CASE STUDY

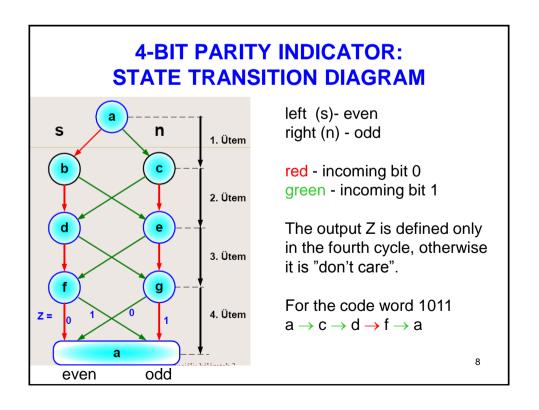

- Synthetize a network which determines the parity of a four bit serial code word.

- Should indicate the parity of the incoming code word after receiving the 4-th bit as

- 1 if the parity is odd,

- 0 if the parity is even.

- The output is irrelevant (don't care) during the first three cycle of the period.

This design project being rather elementary will be skipped now, however it can be read in the Moodle files. Instead of it a more complex problem, a traffic control system will be presented and discussed.

|   |                |                       | S                     | TATE                  | ENCODING                                                                                 |

|---|----------------|-----------------------|-----------------------|-----------------------|------------------------------------------------------------------------------------------|

| q | l <sup>n</sup> | <b>Q</b> <sub>1</sub> | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>3</sub> | • In the firs row, we make use of                                                        |

| 8 | a              | 0                     | 0                     | X                     | the redundancy.                                                                          |

| k | b              | 0                     | 1                     | 0                     | <ul> <li>To the states in the same level<br/>of the state transition diagram,</li> </ul> |

|   | e              | 0                     | 1                     | 1                     | the same Q1 and Q2 codes are ascribed.                                                   |

| Ċ | ł              | 1                     | 1                     | 0                     | • Q1, Q2: cycle counters.                                                                |

|   | e              | 1                     | 1                     | 1                     | • Q3: indicates whether the                                                              |

| 1 | f              | 1                     | 0                     | 0                     | system is in the even or on the                                                          |

| Ę | 5              | 1                     | 0                     | 1                     | odd branch of the state transition diagram.                                              |

|   |                |                       |                       |                       | 12                                                                                       |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                             | Z |

|-----------------------------------------------------------------------------------|---|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                             |   |

| 1 0 0 1 <b>a b</b> 0 1 0                                                          |   |

|                                                                                   | х |

| 2 0 1 0 <b>b d</b> 1 1 0                                                          | х |

|                                                                                   | х |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                             | х |

| 4 1 0 0 <b>f a</b> 0 0 x                                                          | 0 |

| 5 1 0 1 <b>g a</b> 0 0 x                                                          | 1 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                             | х |

| 7         1         1         1         e         g         1         0         1 | х |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                           | STA | TE | E F         | UN                    |                       | ON<br>UN              |    |                  | ΉE                    | οι             | JTP                   | UT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|-------------|-----------------------|-----------------------|-----------------------|----|------------------|-----------------------|----------------|-----------------------|----|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                            |     |    | n-edik ütem |                       |                       |                       |    | (n+1)-edik ütem  |                       |                |                       | 7  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                            | 1   |    | X           | <b>Q</b> <sub>1</sub> | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>3</sub> | qn | q <sup>n+1</sup> | <b>Q</b> <sub>1</sub> | $\mathbf{Q}_2$ | <b>Q</b> <sub>3</sub> | L  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                            | 8   |    | T           | 0                     | 0                     | 0                     | a  | с                | 0                     | 1              | 1                     | X  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                            | 9   |    |             | 0                     | 0                     | 1                     | a  | с                | 0                     | 1              | 1                     | X  |

| 12       1       0       0       f       a       0       0       x       1         13       1       0       1       g       a       0       0       x       1         14       1       1       0       d       g       1       0       1       x | 10  | 0  |             | 0                     | 1                     | 0                     | b  | e                | 1                     | 1              | 1                     | X  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                            | 11  | 1  |             | 0                     | 1                     | 1                     | с  | d                | 1                     | 1              | 0                     | х  |

| 14     1     1     0     d     g     1     0     1     x                                                                                                                                                                                         | 12  | 2  | ł           | 1                     | 0                     | 0                     | f  | a                | 0                     | 0              | X                     | 1  |

|                                                                                                                                                                                                                                                  | 13  | 3  |             | 1                     | 0                     | 1                     | g  | a                | 0                     | 0              | X                     | 0  |

|                                                                                                                                                                                                                                                  | 14  | 4  |             | 1                     | 1                     | 0                     | d  | g                | 1                     | 0              | 1                     | X  |

| 15 1 1 1 <b>e f</b> 1 0 0 x                                                                                                                                                                                                                      | 15  | 5  |             | 1                     | 1                     | 1                     | e  | f                | 1                     | 0              | 0                     | X  |

### EXCITATION TABLE OF THE JK FLIP-FLOP

The logic synthesis is based on the excitation table of the flipflop chosen for the implementation.

| Q <sup>n</sup> | $\rightarrow$ | Q <sup>n+1</sup> | J | K |

|----------------|---------------|------------------|---|---|

| 0              | $\rightarrow$ | 0                | 0 | Х |

| 0              | $\rightarrow$ | 1                | 1 | Х |

| 1              | $\rightarrow$ | 0                | Х | 1 |

| 1              | $\rightarrow$ | 1                | Х | 0 |

|                |               |                  |   |   |

### IMPLEMENTATION ALTERNATIVE USING D FLIP-FLOPS

$$D_1 = Q_2 \qquad \qquad D_2 = Q_1$$

$$D_3 = X \overline{Q}_1 + X \overline{Q}_3 + \overline{X} Q_1 Q_2$$

Due to the "clever" sate encoding, the control of the two flipflops acting as the cycle counter corresponds to the usual one. However the control network of the third flip-flop is somewhat more complex than in the former implementation.

## <section-header><text><text><text><text><page-footer>

|         | ST              | ATE             | TRA             | NSIT            | ION               | TAB    | LE                |                   |

|---------|-----------------|-----------------|-----------------|-----------------|-------------------|--------|-------------------|-------------------|

| Minterm | Q3 <sup>n</sup> | Q2 <sup>n</sup> | Q1 <sup>n</sup> | Q0 <sup>n</sup> | Q3 <sup>n+1</sup> | Q2 n+1 | Q1 <sup>n+1</sup> | Q0 <sup>n+1</sup> |

| index   |                 |                 |                 |                 | D3                | D2     | D1                | D0                |

| 0       | 0               | 0               | 0               | 0               | 0                 | 0      | 0                 | 1                 |

| 1       | 0               | 0               | 0               | 1               | 0                 | 0      | 1                 | 1                 |

| 3       | 0               | 0               | 1               | 1               | 0                 | 0      | 1                 | 0                 |

| 2       | 0               | 0               | 1               | 0               | 0                 | 1      | 1                 | 0                 |

| 6       | 0               | 1               | 1               | 0               | 0                 | 1      | 1                 | 1                 |

| 7       | 0               | 1               | 1               | 1               | 0                 | 1      | 0                 | 1                 |

| 5       | 0               | 1               | 0               | 1               | 0                 | 1      | 0                 | 0                 |

| 4       | 0               | 1               | 0               | 0               | 1                 | 1      | 0                 | 0                 |

| 12      | 1               | 1               | 0               | 0               | 1                 | 1      | 0                 | 1                 |

| 13      | 1               | 1               | 0               | 1               | 1                 | 1      | 1                 | 1                 |

| 15      | 1               | 1               | 1               | 1               | 1                 | 1      | 1                 | 0                 |

| 14      | 1               | 1               | 1               | 0               | 1                 | 0      | 1                 | 0                 |

| 10      | 1               | 1               | 1               | 0               | 1                 | 0      | 1                 | 1                 |

| 11      | 1               | 1               | 1               | 1               | 1                 | 0      | 0                 | 1                 |

| 9       | 1               | 1               | 0               | 1               | 1                 | 0      | 0                 | 0                 |

| 8       | 1               | 0               | 0               | 0               | 0                 | 0      | 0                 | 0                 |

Г

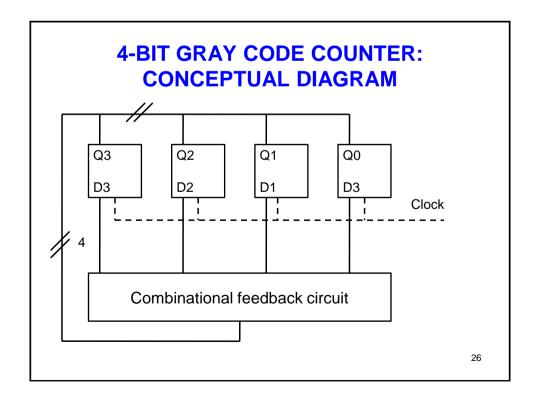

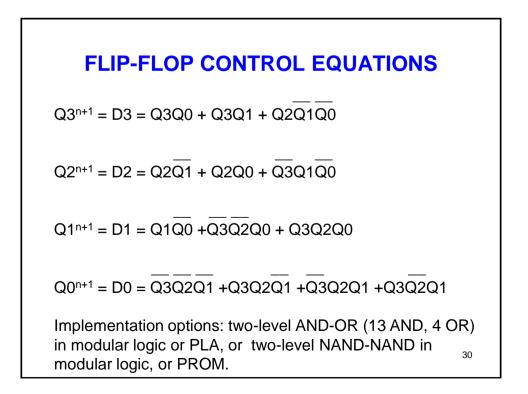

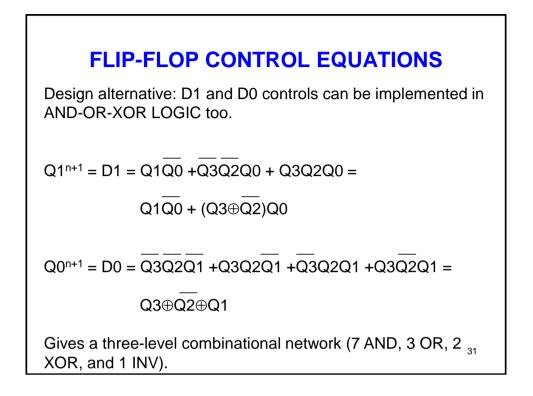

### 4-BIT BI-DIRECTIONAL GRAY CODE COUNTER

Features of design provided by one of the students of my previous course.

Compared designs using D or T flip-flops.

Using T flip-flops, some several common terms could be realized by XOR gate or XOR gate and inverter, leading to further simplification of the feedback circuit.

Complexity: 16 NAND gates (2,3 or 4 inputs), 2 XOR gates and 2 inverters.

Estimated the maximum clock frequency of the counter when using high speed CMOS logic components.

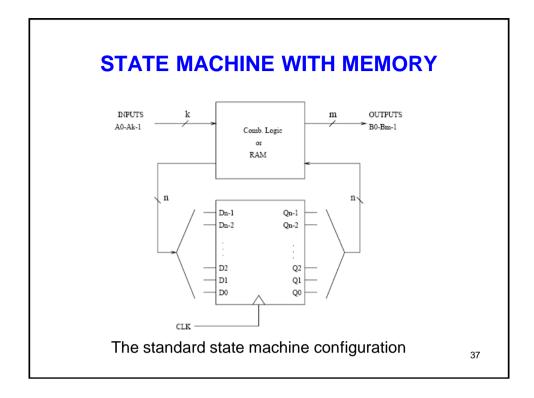

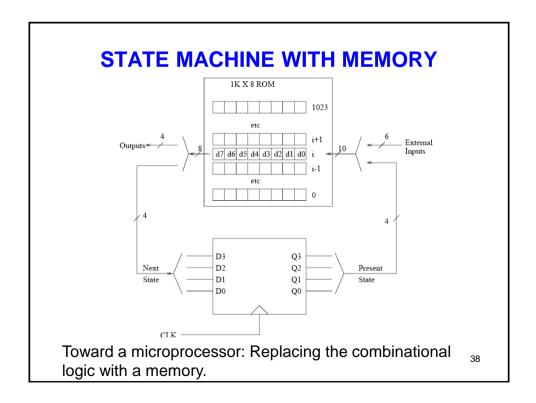

### **STATE MACHINE WITH MEMORY**

To start with, let's assume a state machine with no external inputs or outputs. Then the state machine's *present state* (PS) becomes an address which is input to the ROM. The data word stored in the ROM at that address then corresponds to the *next state* (NS). This correspondence had been initially programmed into the ROM, just as the specic combinational logic in an old state machine had to be pre-determined. So if the PS as defined at the data register are, for example, 1001, then the ROM data word at address 1001 will be the NS which is then passed back to the register. When there are also external inputs, as there will be for most anything of interest, these are combined with the PS bits to form a longer address for the ROM. Similarly, any external outputs are combined with the NS bits in the data word.

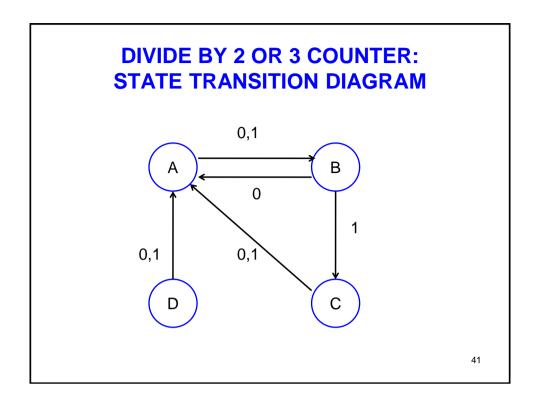

| EXAMPL                           | E: DIVIDE BY                                                           | 2 (  | DR 3     | COL    | JNT | ER       |   |

|----------------------------------|------------------------------------------------------------------------|------|----------|--------|-----|----------|---|

| depending up                     | iter which either div<br>on the value of an e<br>quired, use 2 bits, o | xter | nal inp  | ut bit | P.  |          |   |

| Α (                              | 00                                                                     |      | Present  | State  | Nex | t State  |   |

|                                  | )1                                                                     | p    | $Q_1Q_0$ |        |     | $D_1D_0$ | r |

|                                  |                                                                        | 0    | 00       | А      | В   | 01       | 0 |

| -                                | 10                                                                     | 0    | 01       | В      | Α   | 00       | 1 |

| D ´                              | 11                                                                     | 0    | 10       | С      | Α   | 00       | 0 |

|                                  |                                                                        | 0    | 11       | D      | Α   | 00       | 0 |

| P = 0                            | divide by 2                                                            | 1    | 00       | А      | В   | 01       | 0 |

| P = 1                            | divide by 3                                                            | 1    | 01       | В      | C   | 10       | 1 |

|                                  |                                                                        | 1    | 10       | С      | Α   | 00       | 0 |

| Output R =1 if                   | present state is B,                                                    | 1    | 11       | D      | А   | 00       | 0 |

| otherwise R =<br>State D is norr | -                                                                      |      |          |        |     | 40       |   |

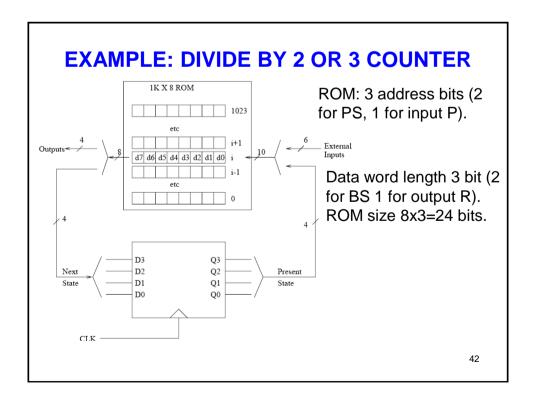

### **EXAMPLE: DIVIDE BY 2 OR 3 COUNTER**

The programming of the ROM is straightforward and can be read directly from the truth table. Addresses are encoded as  $PQ_{1}Q_{0}$ and the data words as  $D_1 D_0 R$ . For example take the 5th row of the truth table. The address would be 100 and the data word at this address would be 010. The remaining bits of the ROM would be programmed in the same way. So one would initially "burn in" these bit patterns into the ROM and put it into the circuit.

|   | Present  | : State | Nex | t State  |   |

|---|----------|---------|-----|----------|---|

| p | $Q_1Q_0$ |         |     | $D_1D_0$ | r |

| 0 | 00       | А       | В   | 01       | 0 |

| 0 | 01       | В       | Α   | 00       | 1 |

| 0 | 10       | С       | Α   | 00       | 0 |

| 0 | 11       | D       | Α   | 00       | 0 |

| 1 | 00       | Α       | В   | 01       | 0 |

| 1 | 01       | В       | С   | 10       | 1 |

| 1 | 10       | С       | Α   | 00       | 0 |

| 1 | 11       | D       | Α   | 00       | 0 |

|   | I        |         |     |          |   |

|   |          |         |     |          |   |

|   |          |         |     |          |   |

|   |          |         |     |          |   |

|   |          |         |     | 43       |   |

|   |          |         |     |          |   |

### **GENERALIZATION TO** MICROPROCESSORS

A state machine with zero input bits can perform a counterlike function, but not more: its next state is limited to be a function only of the present state. A single input bit can be used to "program" the state machine to behave in one of two possible ways for each present state, as was illustrated with the examples.

E.g. in an up/down counter.

On the other hand, with n inputs, the machine can perform  $2^{n}$  different operations. So, e.g. with n = 8 the machine can perform one of 256 different operations on each clock cycle. This allows for tremendous potential and flexibility. 44

### GENERALIZATION TO MICROPROCESSORS

The input bits can themselves be sequenced and stored externally in a specific sequence which is then applied step by step to the state machine inputs on successive clock cycles. Such a stored sequence of operations is a program and the 256 operations represent the programming operations.

Here we have essentially configured a simple micro-processor. The inputs and outputs would need to be connected to buses (via 3-state buffers where appropriate), which in turn are also connected to memories which store the program and any output or input data. The buses would also be connected to various input/output devices, mass storage devices, etc.

45

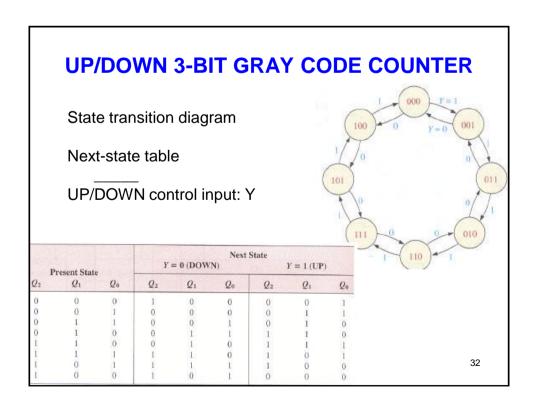

### SYNTHESIS OF SYNCHRONOUS CIRCUITS: RECAPITULATION

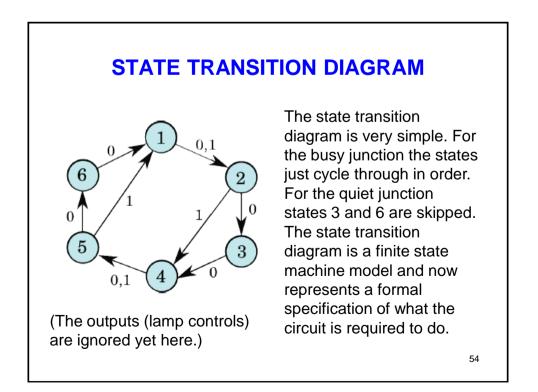

- 1. Constructing the state transition diagram.

- 2. Selection or specifying the encoding of the states.

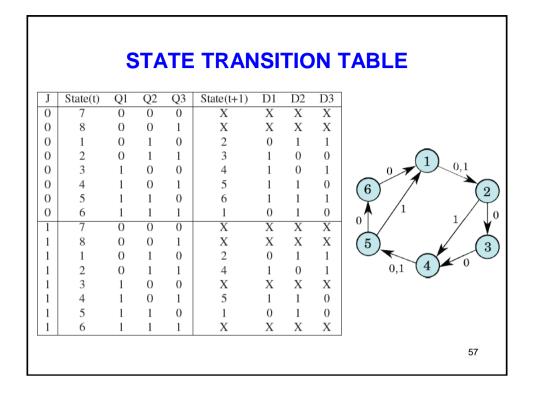

- 3. Constructing the state transition tables. It gives for each cycle the next-state of each flip-flop in the function of the previous states of all flip-flops and in the function of the control conditions (up/down).

- 4. Selection or specifying the type of flip-flop used in the implementation. Excitation table of the flip-flop type.

- 5. Determination of the logic functions of the control input(s) of each flip-flop. Performing the necessary or appropriate minimization.

- 6. Selection of the types of logic gates to be used and implementation of the feedback/control network.

### <text><text><text>

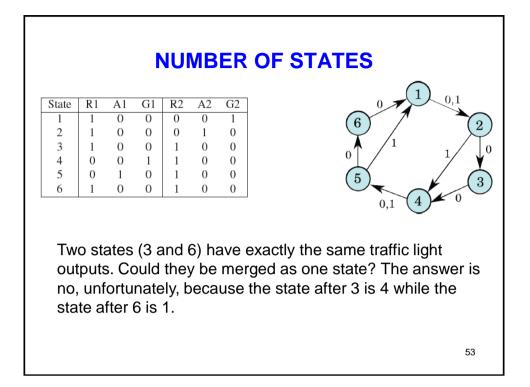

### FLIP-FLOPS: TYPE AND NUMBER

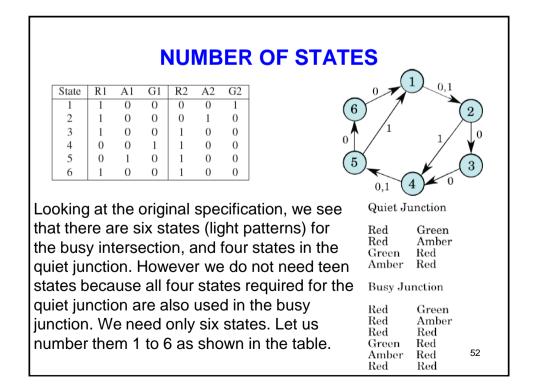

Since the number of states is equal to six, the minimum number of flip-flops, which can support six states, is three.

The maximum number of flip-flops one may use is six (one flip-flop per state), though this implementation would clearly be wasteful and so we will use three D-type flip-flops. There will be two unused states.

55

# <section-header><text><text><text>

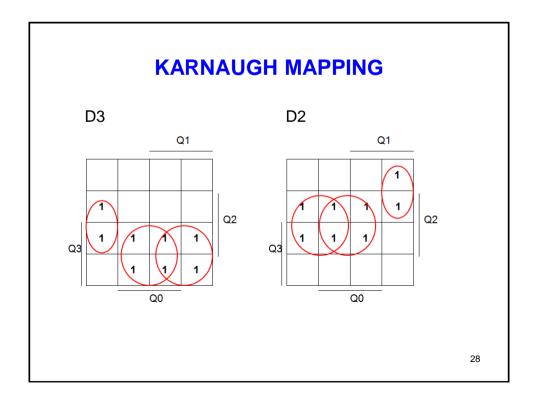

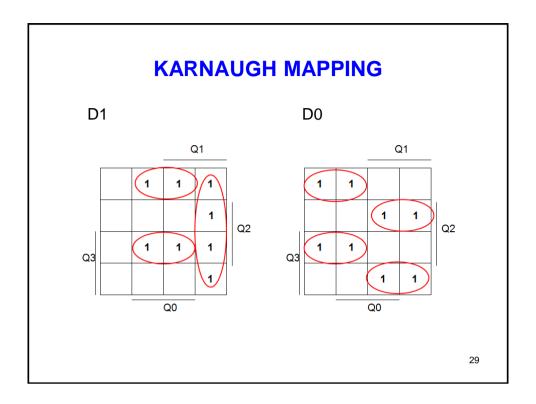

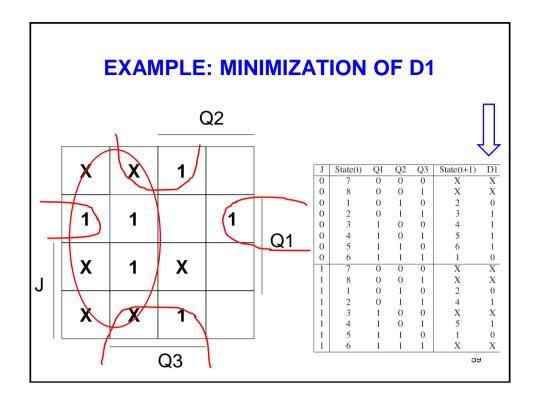

### **MINIMIZATION ON KARNAUGH MAP**

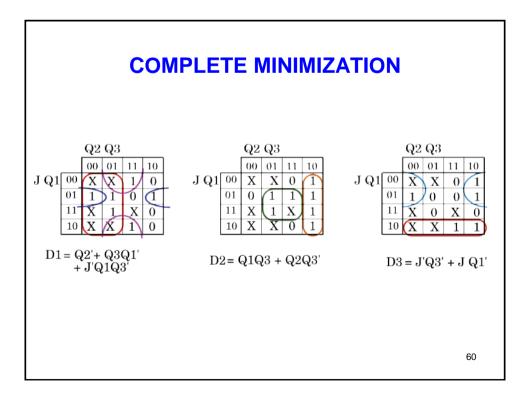

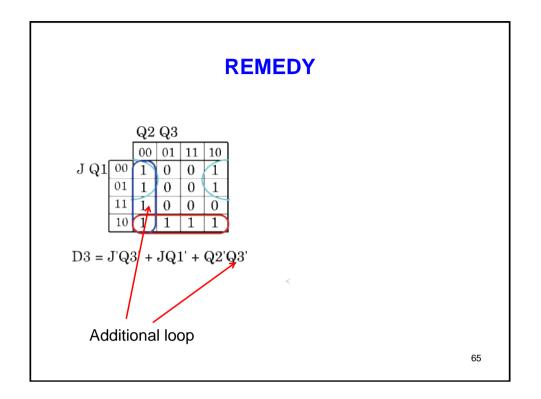

The next step is to determine the required logic expressions for the three flip-flop inputs D1, D2, and D3.

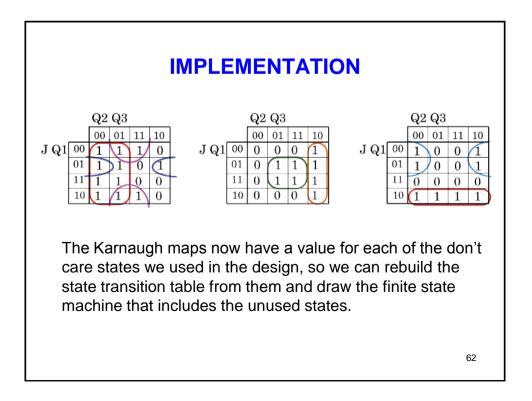

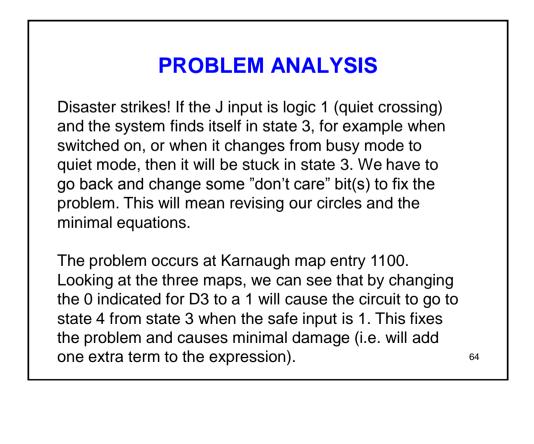

Once the minimization has been done, we can replace the "don't care" outputs in the Karnaugh maps with the actual values we will get out of the circuit. Any don't care inside a circle is replaced with 1, and any outside all circles is replaced with 0.

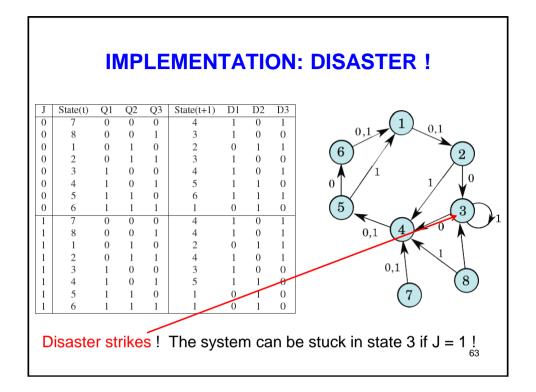

We have now a completely defined a sequential circuit and we should check whether the system behaves correctly even if it starts from one of the unused states. A convenient way of checking this is by constructing the complete transition diagram in which the unused states 7 and 8 are also included.

### FURTHER MODIFICATIONS: DIFFERENT STATE ASSIGNMENTS

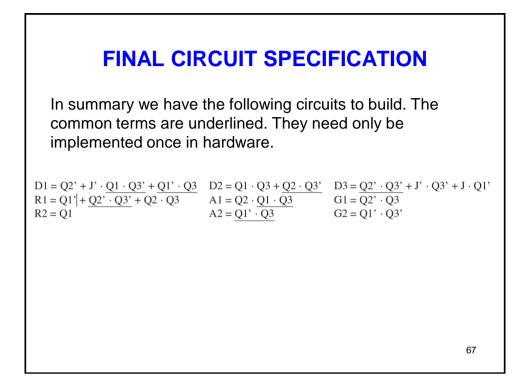

If we want to try to find a simpler overall circuit, we may try different flip-flop assignments for the states. One idea is to minimize the output circuitry. We could, for example, make R1=Q1 and R2=Q2, if these simple assignments will give us a correct complete state assignment. The third output, Q3 has to be assigned such that all used states are distinct. One possible set of assignments are shown below:

| tate Q1                          | Q2      | Q3   | R1    | A1     | G1     | R2   | A2    | G2 |

|----------------------------------|---------|------|-------|--------|--------|------|-------|----|

|                                  | 0       | 0    |       | 0      | 0      | 0    | 0     | 1  |

| 2 1                              | 0       | 1    |       | 0      | 0      | 0    | 1     | 0  |

| 3 1                              | 1       | 1    | 1     | 0      | 0      | 1    | 0     | 0  |

| 4 0                              | 1       | 1    | 0     | 0      | 1      | 1    | 0     | 0  |

| 5 0                              | 1       | 0    | 0     | 1      | 0      | 1    | 0     | 0  |

| 6 1                              | 1       | 0    | 1     | 0      | 0      | 1    | 0     | 0  |

| 7 0                              | 0       | 0    | Х     | Х      | Х      | Х    | Х     | Х  |

| 8 0                              | 0       | 1    | Х     | Х      | Х      | Х    | Х     | Х  |

| out circu<br>we have<br>with the | e to re | desi | gn th | ie sta | ite se | quei | ncing |    |

|   |   | NE       | EW | S  | ΓΑ | TE T/      | AB | LE | S  |  |

|---|---|----------|----|----|----|------------|----|----|----|--|

| [ | J | State(t) | Q1 | Q2 | Q3 | State(t+1) | D1 | D2 | D3 |  |

|   | 0 | 7        | 0  | 0  | 0  | X          | X  | X  | X  |  |

|   | 0 | 8        | 0  | 0  | 1  | Х          | Х  | Х  | Х  |  |

|   | 0 | 1        | 1  | 0  | 0  | 2          | 1  | 0  | 1  |  |

|   | 0 | 2        | 1  | 0  | 1  | 3          | 1  | 1  | 1  |  |

|   | 0 | 3        | 1  | 1  | 1  | 4          | 0  | 1  | 1  |  |

|   | 0 | 4        | 0  | 1  | 1  | 5          | 0  | 1  | 0  |  |

|   | 0 | 5        | 0  | 1  | 0  | 6          | 1  | 1  | 0  |  |

|   | 0 | 6        | 1  | 1  | 0  | 0          | 1  | 0  | 0  |  |

|   | 1 | 7        | 0  | 0  | 0  | Х          | Х  | Х  | Х  |  |

|   | 1 | 8        | 0  | 0  | 1  | Х          | Х  | Х  | Х  |  |

|   | 1 | 1        | 1  | 0  | 0  | 2          | 1  | 0  | 1  |  |

|   | 1 | 2        | 1  | 0  | 1  | 4          | 0  | 1  | 1  |  |

|   | 1 | 3        | 1  | 1  | 1  | Х          | Х  | Х  | X  |  |

|   | 1 | 4        | 0  | 1  | 1  | 5          | 0  | 1  | 0  |  |

|   | 1 | 5        | 0  | 1  | 0  | 1          | 1  | 0  | 0  |  |

|   | 1 | 6        | 1  | 1  | 0  | Х          | Х  | Х  | Х  |  |

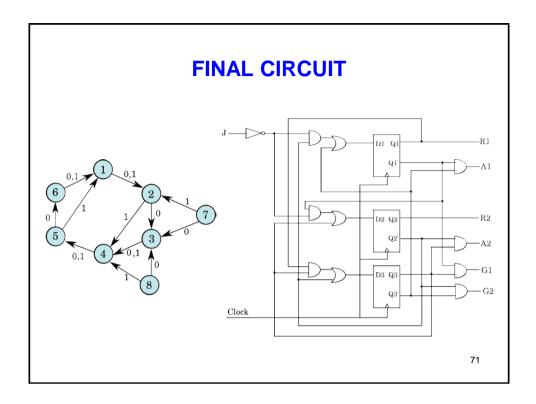

the don't care states - which you can do as an exercise - it turns out to be safe. The final state diagram and circuit looks like this:

### **PROBLEMS AND EXERCISES**

1. In a complete state machine, all possible transitions between states of a finite state machine (FSM) should be specified. Your state machine has two inputs, A and B, and two states, S0 and S1. You are told that your FSM behaves as follows:

The FSM moves from S0 to S1 if and only if A = 1. The FSM moves from S1 to S0 if and only if A = 0 and B = 1. Draw the complete state transition diagram of your FSM.

2. Analyze the operation of the type 7474 edge triggered D flip-flop and give its full operational/truth table for asynchronous and synchronous control.

73

### **PROBLEMS AND EXERCISES**

3. Design a finite state machine which determines whether the two 4-bit binary numbers arriving simultaneously on the two inputs are equal or not. If not, it should also indicate which is the greater. The codewords in pairs arrive cyclically to the **X** and Y inputs of the circuit. The MSBs arrive at first to the input.

4. Four-bit codewords representing normal BCD coded decimal digits arrive cyclically to the **X** input of a synchronous sequential circuit. The MSB arrives first. Design a synchronous sequential circuit which indicates with 1 on its **Z** output if the arriving 4-bit codeword presumably representing a normal BCD digit is invalid.

### PROBLEMS AND EXERCISES

5. Design a synchronous sequential circuit to control a bottled drink vending machine. A bottle of drink costs 200 HUF. The machine accepts 50, 100, and 200 HUF coins. When the amount of money inserted equals or exceeds the price of the merchandize, the machine vends a bottle and returns change if any, then waits for the next transaction.

6. Design a synchronous counter according to the specifications given below:

Encoding: Excess-3 (Stibitz) code Counting direction: up or down, externally controllable Mode of operation: self-correcting (returns to the

counting cycle from the invalid states).