# DIGITAL TECHNICS Dr. Bálint Pődör Óbuda University, Microelectronics and Technology Institute 11. LECTURE: TRENDS IN DIGITAL LOGIC CIRCUITS ISt (Aufumn) term 2018/2019

# DEVELOPMENT

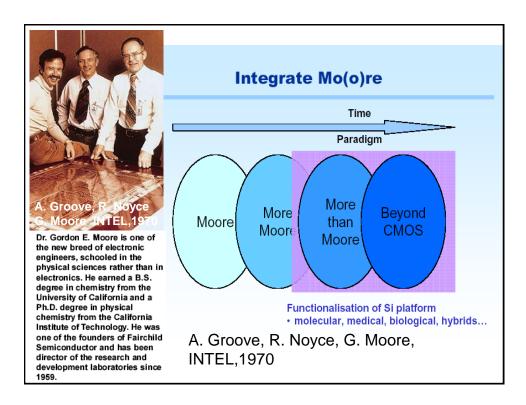

Soon after Bardeen, Brattain, and Shockley invented a solidstate device in 1947 to replace electron vacuum tubes, the microelectronics industry and a revolution started.

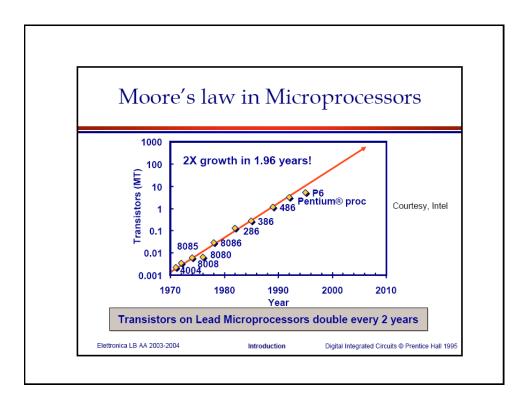

Since its birth, the industry has experienced six decades of unprecedented explosive growth driven by two factors:

*Noyce* and *Kilby* inventing the planar integrated circuit and the advantageous characteristics that result from scaling (shrinking) solid-state devices.

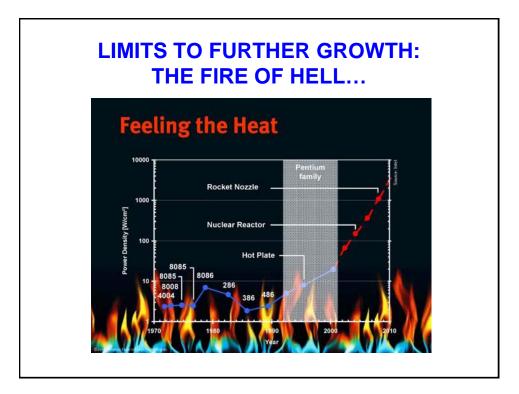

# **CHALLENGES**

Scaling solid-state devices has the peculiar property of improving cost, performance, and power, which has historically given any company with the latest technology a large competitive advantage in the market.

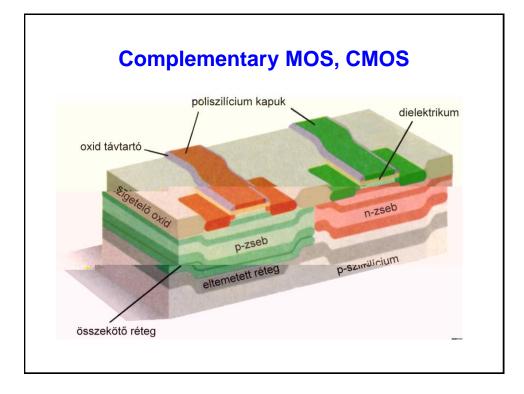

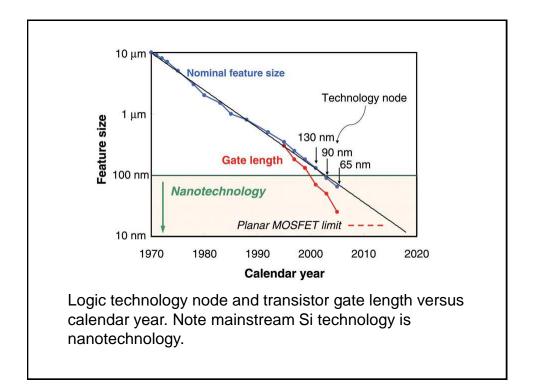

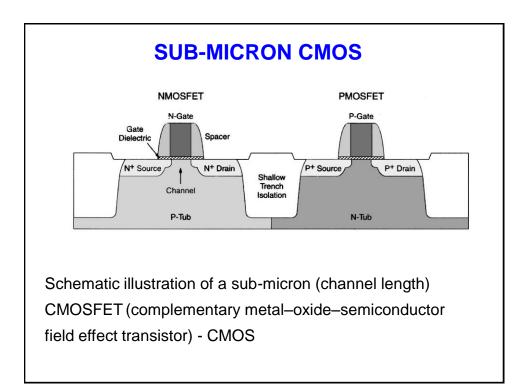

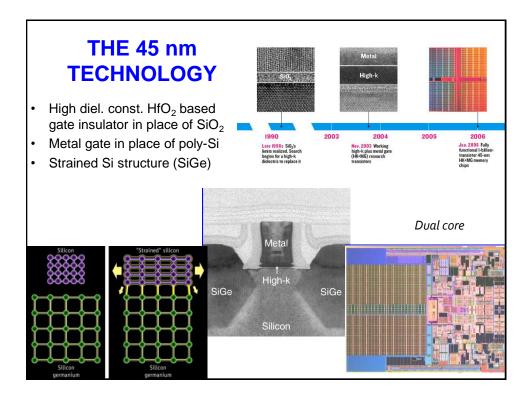

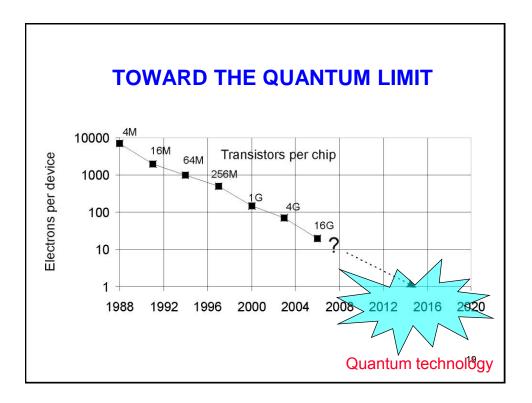

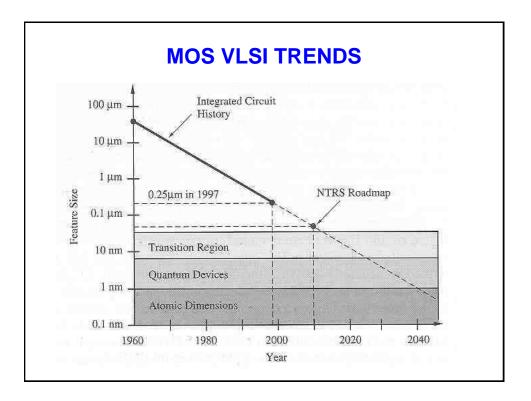

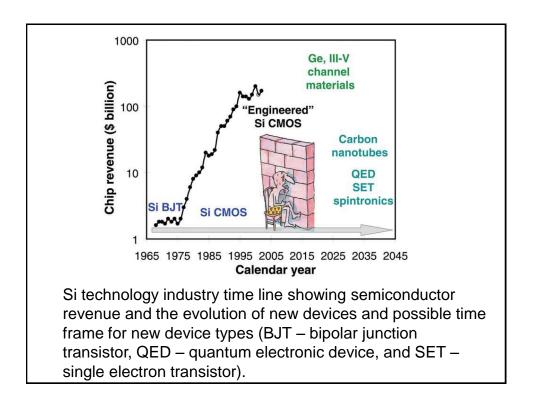

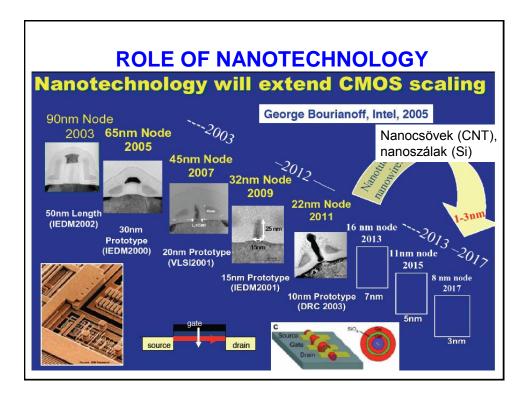

As a result, the microelectronics industry has driven transistor feature size scaling from 10  $\mu$ m to ~30 nm during the past 50 years. During most of this time, scaling simply consisted of reducing the feature size. However, during certain periods, there were major changes as with the industry move from Si bipolar to p-channel metal-oxide semiconductor (MOS), then to n-channel MOS, and finally to complementary MOS (CMOS) planar transistors in the 1980s, which has remained the dominate technology for the past two decades.

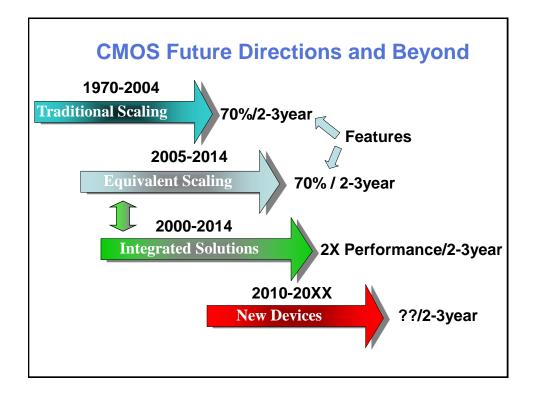

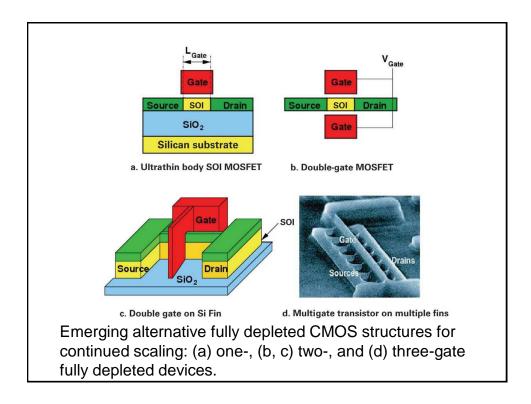

The big challenge going forward is that the end of planar CMOS transistor scaling is near as the transistor size approaches tens of nanometers. How the industry evolves after this limit is reached is unclear.

# CHALLENGES AND POSSIBLE ANSWERS

The big challenge going forward is that the end of planar CMOS transistor scaling is near as the transistor size approaches tens of nanometers. How the industry evolves after this limit is reached is unclear.

To address these challenges, present day research is focused on identifying new materials and devices that can augment and/or potentially replace the aging ~50-year-old Si transistor.

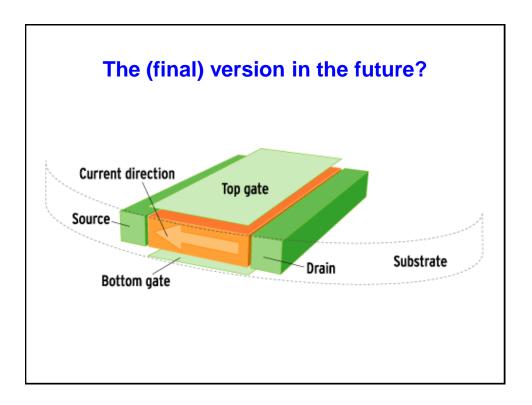

Two approaches under investigation are: (1) nonclassical CMOS, which consists of new channel materials and/or multigate fully depleted device structures;

and

(2) alternatives to CMOS, such as *carbon based electronics*, *spintronics*, *single electron devices*, and *molecular computing*.

# THE MOSFET AND CMOS INTEGRATED CIRCUITS

The Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET) is (still) the prevailing device in microprocessors and memory circuits.

The MOSFET's advantages over other types of devices are its (i) mature fabrication technology, (ii) its successful scaling characteristics and (iii) complementary MOSFETs yielding CMOS circuits.

The fabrication process of silicon devices has evolved over the last 40 years into a mature, reproducible and reliable integrated circuit manufacturing technology.

| TECHNOLOGY SCALING                                |      |              |      |      |      |      |  |  |

|---------------------------------------------------|------|--------------|------|------|------|------|--|--|

|                                                   |      |              |      |      |      |      |  |  |

| Year of Introduction                              | 1994 | <b>199</b> 7 | 2000 | 2003 | 2006 | 200  |  |  |

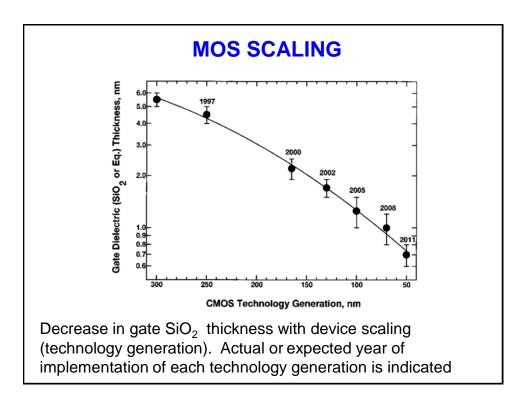

| Channel length (µm)                               | 0.4  | 0.3          | 0.25 | 0.18 | 0.13 | 0.1  |  |  |

| Gate oxide (nm)                                   | 12   | 7            | 6    | 4.5  | 4    | 4    |  |  |

| V <sub>DD</sub> (V)                               | 3.3  | 2.2          | 2.2  | 1.5  | 1.5  | 1.5  |  |  |

| $V_T(\mathbf{V})$                                 | 0.7  | 0.7          | 0.7  | 0.6  | 0.6  | 0.6  |  |  |

| NMOS $I_{Dsat}$ (mA/µm)<br>(@ $V_{GS} = V_{DD}$ ) | 0.35 | 0.27         | 0.31 | 0.21 | 0.29 | 0.33 |  |  |

| PMOS $I_{Dsat}$ (mA/µm)<br>(@ $V_{GS} = V_{DD}$ ) | 0.16 | 0.11         | 0.14 | 0.09 | 0.13 | 0.16 |  |  |

: 1999, and 2001 http://public.itrs.net/

| Year                                    | 2001 | 2005  | 2007 | 2010 | 2016 |

|-----------------------------------------|------|-------|------|------|------|

| Half<br>module<br>(nm)                  | 150  | 100   | 80   | 55   | -    |

|                                         | 130  | 80    | 65   | 45   | 22   |

| Alignment<br>accuracy                   | 50   | 35    | 25   | 20   | 15   |

|                                         | 46   | 28    | 23   | 18   | 9    |

| T <sub>oxid</sub><br>equivalent<br>(nm) | 1.6  | 1-1.5 | 1    | 0.8  | 0.5  |

|                                         | 1.4  | 1.0   | 0.8  | 0.6  | 0.4  |

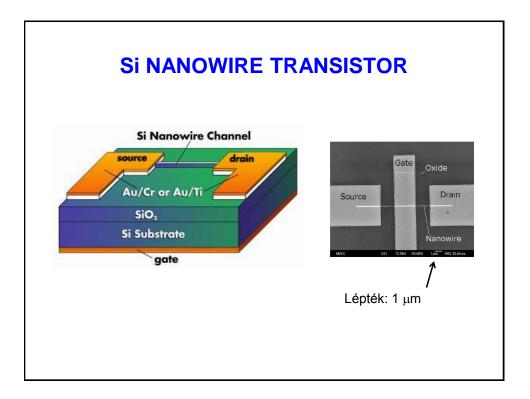

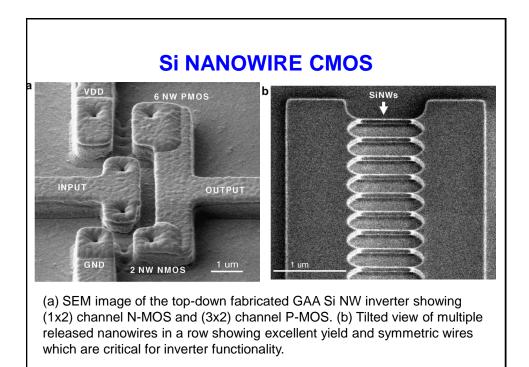

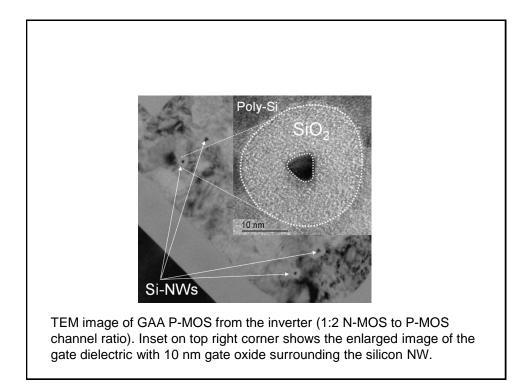

# Si NANOWIRE GATE-ALL-AROUND TRANSISTOR

The foremost issues are:

1. poor gate electrostatic control of the channel potential and thus degraded short-channel effects;

2. high gate leakage due to thin gate dielectric;

3. reduced channel mobility on account of increased doping in the channel; and

4. increased source/drain resistance.

These issues cause higher off-state leakage and limit the drive current leading to compromised performance, defeating the main purpose of scaling.

| statement of the                                                                                             | Contents lists available at ScienceDirect                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 261                                                                                                          | Solid-State Electronics                                                                                                                                                                     |

| ELSEVIER                                                                                                     | journal homepage: www.elsevier.com/locate/sse                                                                                                                                               |

| and top-down approact<br>K.D. Buddharaju *, N. Singh, S                                                      | .C. Rustagi, Selin H.G. Teo, G.Q. Lo, N. Balasubramanian, D.L. Kwong                                                                                                                        |

| and top-down approact<br>K.D. Buddharaju *, N. Singh, S<br>Istitute of Microelectronics. (A*STAR) Agency for | h                                                                                                                                                                                           |

| and top-down approac<br>K.D. Buddharaju*, N. Singh, S                                                        | h<br>.C. Rustagi, Selin H.G. Teo, G.Q. Lo, N. Balasubramanian, D.L. Kwong<br>Science, Technology and Research, 11 Science Park Road, Singapore Science Park II, 117685 Singapore, Singapore |

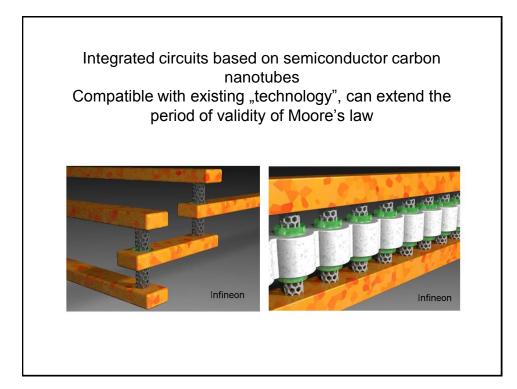

# **CNT BASED ELECTRONICS**

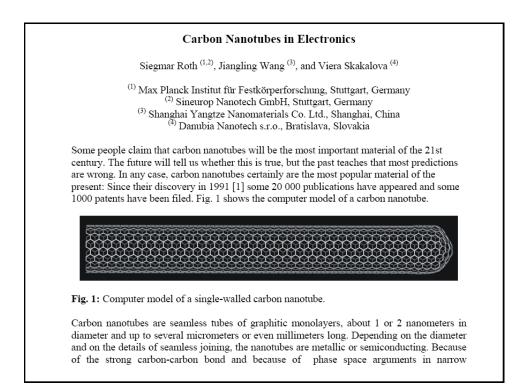

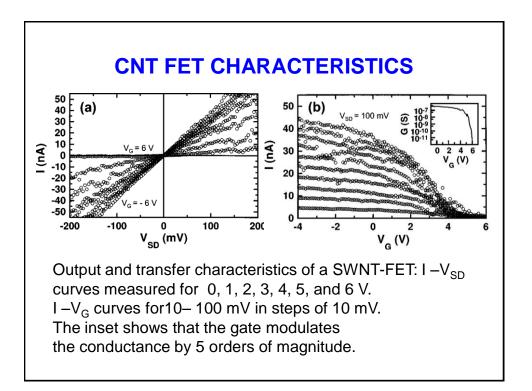

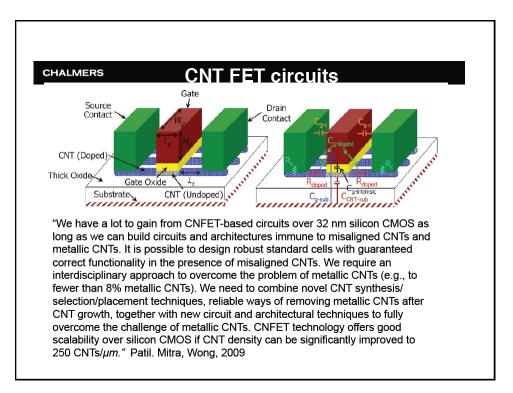

Carbon based nanoelectronics are officially recommended by the International Technology Roadmap for Semiconductor (ITRS) in 2009 as the most promising technology for further electronics to extend the Moore law. In particular, carbon nanotube (CNT) is an exceptionally good electronic material with extremely high carrier mobility, long mean free length, and the smallest body, which may potentially bring the CNT based field-effect transistors (FETs) and integrated circuits (ICs) outstanding performances, including high speed and low power dissipation.

# **CNT BASED ELECTRONICS**

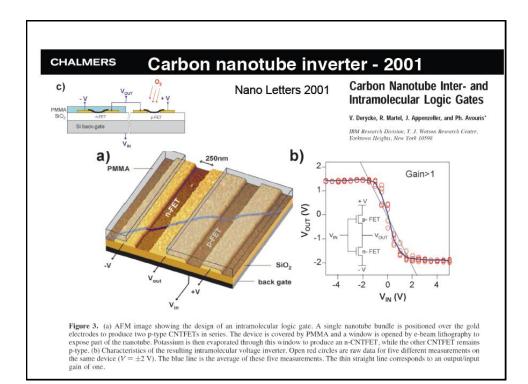

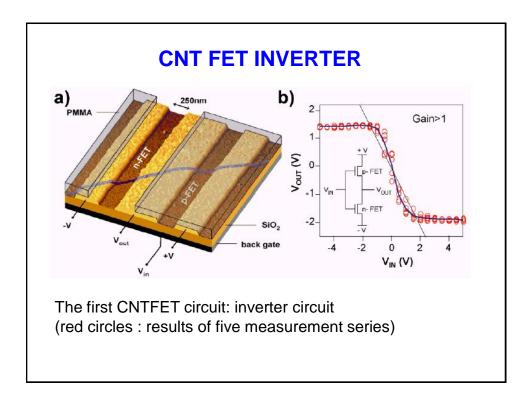

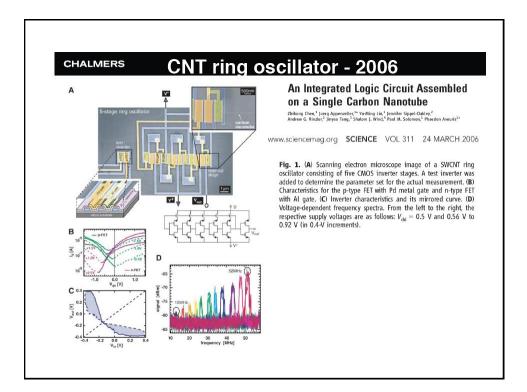

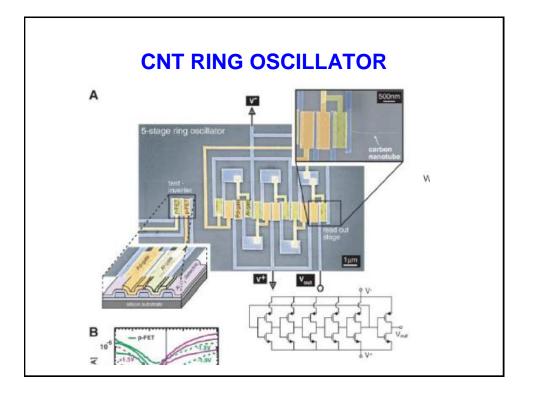

After about 15 years development, various kinds of basic logic gates, arithmetic and control circuits have been realized on CNTs, and extensive investigations have been carried out to explore the potential advantages of CNT based electronics over Si complementary-metal-oxide-semiconductor (CMOS) technology.

# **CARBON BASED (NANO-)ELECTRONICS**

Advantages:

High carrier mobility (fast operation, high cutoff frequency, etc.) Exceptionally small (nano-size) dimensions (őhigh level of integration, etc.) Good heat conduction (high-power devices, etc.) Etc., ...

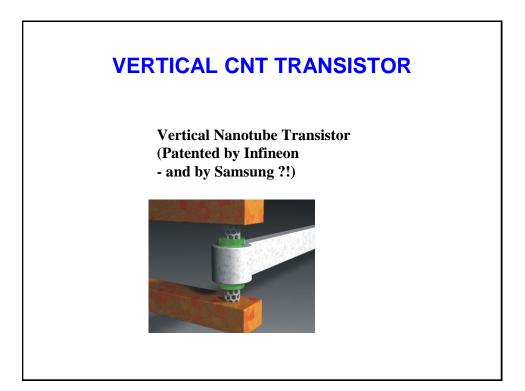

CNT devices (presently in the forefront):

Wires, connections Diode, transistor (FET) Optoelectronic devices Electron emitters (cold-, or field emission)

# **CARBON BASED (NANO-)ELECTRONICS**

Field-effect transistors based on semiconductor *nanotubes* and *graphene nanoribbons* have already been demonstrated, and metallic nanotubes could be used as high-performance iinterconnects.

Moreover, owing to the excellent optical properties of nanotubes it could be possible to make both electronic and optoelectronic devices from the same material.

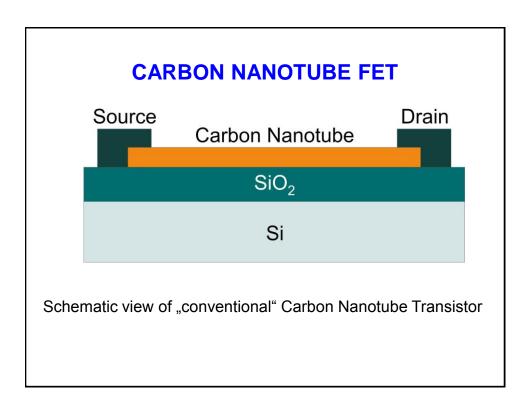

# **CARBON NANOTUBE FET**

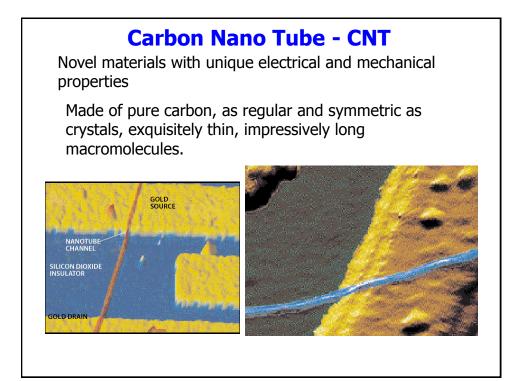

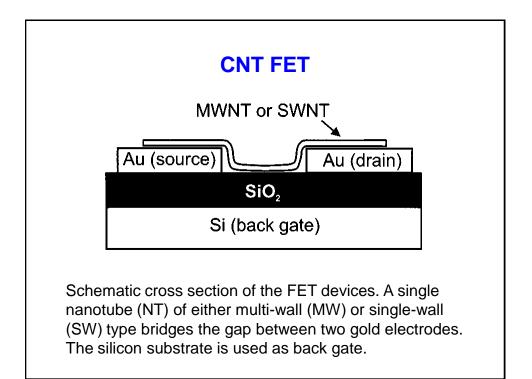

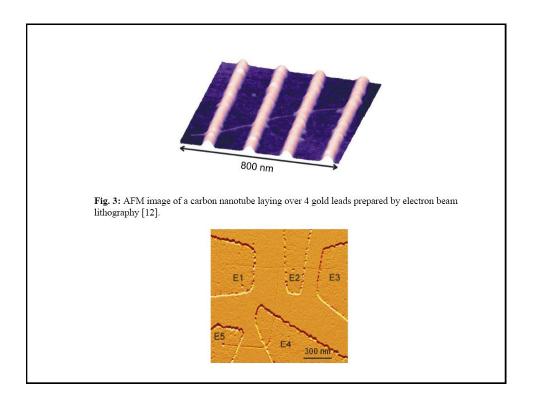

Carbon nanotubes are a new form of carbon with unique electrical and mechanical properties. They can be considered as the result of folding graphite layers into carbon cylinders and may be composed of a single shell–single wall nanotubes, or of several shells—multi-wall nanotubes. Depending on the folding angle and the diameter, nanotubes can be metallic or semiconducting.

Their interesting electronic structure makes carbon nanotubes ideal candidates for novel molecular devices. Metallic NTs, for example, were utilized as Coulomb islands in single-electron transistors and, very recently, several groups built a molecular field-effect transistor (FET) with a semiconducting nanotube.

# **CNT IC: SCALING DOWN**

APPLIED PHYSICS LETTERS 100, 263116 (2012)

# Carbon nanotube based ultra-low voltage integrated circuits: Scaling down to 0.4 V

Li Ding,<sup>1</sup> Shibo Liang,<sup>1</sup> Tian Pei,<sup>1</sup> Zhiyong Zhang,<sup>1,a)</sup> Sheng Wang,<sup>1</sup> Weiwei Zhou,<sup>2</sup> Jie Liu,<sup>2</sup> and Lian-Mao Peng<sup>1,a)</sup> <sup>1</sup>Key Laboratory for the Physics and Chemistry of Nanodevices and Department of Electronics,

Peking University, Beijing 100871, China

<sup>2</sup>Department of Chemistry, Duke University Durham, North Carolina 27708, USA

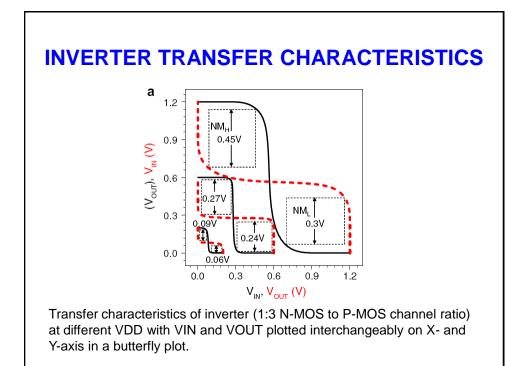

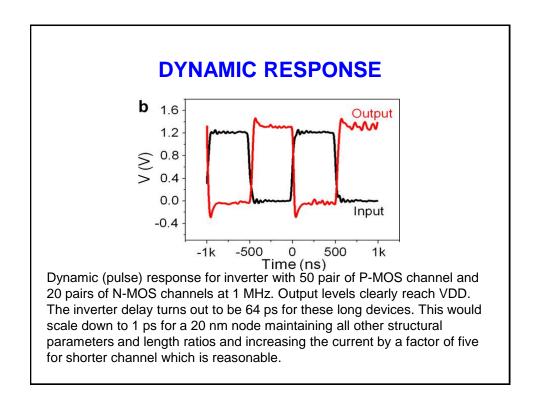

Carbon nanotube (CNT) based integrated circuits (ICs) including basic logic and arithmetic circuits were demonstrated working under a supply voltage low as 0.4 V, which is much lower than that used in conventional silicon ICs. The low limit of supply voltage of the CNT circuits is determined by the degraded noise margin originated from the process inducing threshold voltage fluctuation. The power dissipation of CNT ICs can be remarkably reduced by scaling down the supply voltage, and it is of crucial importance for the further developments of nanoelectronics ICs with higher integration density.

| Si AND CNT INTERCOMPARISON      |                                |                                |                               |                               |                                |                            |                        |                               |  |

|---------------------------------|--------------------------------|--------------------------------|-------------------------------|-------------------------------|--------------------------------|----------------------------|------------------------|-------------------------------|--|

|                                 | CNT<br>FET<br>Seidel<br>(2004) | CNT<br>FET<br>Seidel<br>(2004) | CNT<br>FET<br>Javey<br>(2003) | CNT<br>FET<br>Javey<br>(2004) | CNT<br>FET<br>McEuen<br>(2002) | TriGate<br>Doyle<br>(2003) | FinFET<br>Yu<br>(2002) | SON<br>Harriso<br>n<br>(2003) |  |

| Channel Material                | CNT                            | CNT                            | CNT                           | CNT                           | CNT                            | Si                         | Si                     | Si                            |  |

| Drive Voltage<br>[V]            | 0.4                            | 1.0                            | 0.6                           | 0.4                           | 1.0                            | 1.3                        | 1.2                    | 0.9                           |  |

| Drive Current<br>[mA/µm]        | 15                             | 2.4-6.4                        | 14                            | 11.6                          | 2.96                           | 0.88                       | 0.72                   | 0.914                         |  |

| Transconductance<br>[µS/µm]     | 4000                           | 2640-<br>6430                  | 3070                          | 17650                         | 6666                           | 920                        | 900                    | 1170                          |  |

| Subthreshold Slope<br>[mV/dec]  | 200                            | 105                            | 150-170                       | 110                           | 80                             | 69.5                       | 101                    | 70                            |  |

| On Resistance<br>[Ω/μm]         | 25                             | 155-425                        | 43                            | 22                            | 473                            | 1480                       | 1667                   | 985                           |  |

| Gate Length<br>[nm]             | 20                             | 600                            | 300                           | 50                            | 1400                           | 60                         | 10                     | 70                            |  |

| Gate Oxide<br>Thickness<br>[nm] | 12                             | 8*                             | 67                            | 8                             | 1                              | 1.5                        | 1.7                    | 2                             |  |

| Off Current<br>[nA/µm]          | 1.0                            | 22**                           | 1.0                           | 600                           | N/A                            | 120                        | 20                     | 1                             |  |

# GRAPHENE

#### The evolution of graphene-based electronic devices

Joydeep Basu<sup>a</sup>\*, Jayanta Kumar Basu<sup>b</sup> and Tarun Kanti Bhattacharyya<sup>a</sup>

<sup>a</sup>Department of Electronics and Electrical Communication Engineering; <sup>b</sup>Department of Chemical Engineering, Indian Institute of Technology, Kharagpur 721302, India

(Received 29 April 2010; final version received 21 July 2010)

Successful isolation of single-layer graphene, the two-dimensional allotrope of carbon from graphite, has fuelled a lot of interest in exploring the feasibility of using it for fabrication of various electronic devices, particularly because of its exceptional electronic properties. Graphene is poised to save Moore's law by acting as a successor of silicon-based electronics. This article reviews the success story of this allotrope with a focus on the structure, properties and preparation of graphene as well as its various device applications.

Keywords: electronic device; FET; field effect; graphene; nanoelectronics

Source: Int. J. of Smart and Nano Materials, Aug. 2010

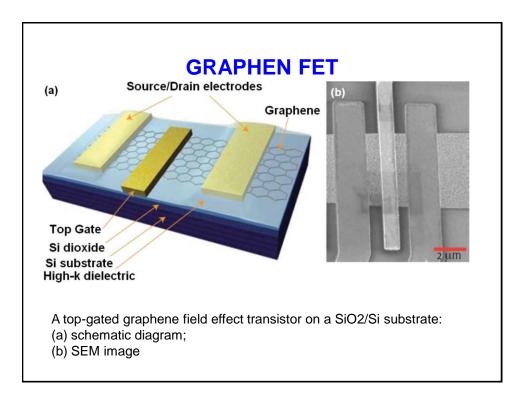

### **GRAPHEN ELECTRONIC DEVICES**

Successful isolation of single-layer graphene, the two-dimensional allotrope of carbon from graphite, has fuelled a lot of interest in exploring the feasibility of using it for fabrication of various electronic devices, particularly because of its exceptional electronic properties.

Graphene is poised to save Moore's law by acting as a successor of silicon-based electronics.

Azért itt is érvényes, hogy a jövő eldönti, hogy ez igaz lesz-e, da a múlt arra tanít, hogy a legtöbb jóslat nem vált be...

# **GRAPHENE PROPERTIES**

Table 1. Comparison of the properties of graphene with those of some common semiconductors.

|                                                                                                           | Graphene | Si   | Ge   | GaAs  | InAs   | InP   |

|-----------------------------------------------------------------------------------------------------------|----------|------|------|-------|--------|-------|

| Electron mobility (cm <sup>2</sup> V <sup><math>-1</math></sup> s <sup><math>-1</math></sup> )<br>@ 300 K | 200,000  | 1400 | 3900 | 4600  | 16,000 | 2800  |

| Band gap energy, $E_g$ (eV)                                                                               | 0        | 1.12 | 0.66 | 1.42  | 0.36   | 1.35  |

| Electron saturation velocity $V_{sat}$<br>(10 <sup>7</sup> cm/s)                                          | >5       | 1    | 0.6  | 2.2   | 4.0    | 2.2   |

| Density-of-states electron<br>effective mass $(m^*/m_0)$                                                  | 0        | 1.08 | 0.56 | 0.067 | 0.023  | 0.077 |

| Relative dielectric constant, er                                                                          | 2.4      | 11.9 | 16.0 | 13.1  | 14.6   | 12.4  |

| Thermal conductivity $(W m^{-1} K^{-1})$                                                                  | 5000     | 150  | 60.2 | 46    | 27     | 68    |

| Lattice constant (Å)                                                                                      | 2.46     | 5.43 | 5.65 | 5.65  | 6.06   | 5.87  |

# FITTING INTO THE Si TECHNOLOGY PROCESS LINE...

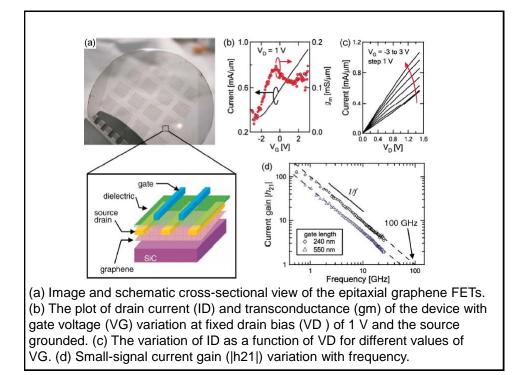

Multilayered epitaxial graphene on insulating SiC substrate has been used for fabricating hundreds of transistors on a single chip. The world's first RF graphene field-effect transistor has been accomplished using 1–2 layered epitaxial graphene on SiC.

Recently, IBM has reported the creation of top-gated transistors using graphene grown on the silicon face of a 2 inch thick SiC wafer that can operate at speeds of 100 GHz with an electron carrier density of about  $3 \times 10^{12}$  cm<sup>-2</sup> and peak mobility of 1500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature.

This far surpasses the performance of the fastest GaAs transistors.

|            | NEW EMERGING LOGIC DEVICES                       |                                                                                                                                                 |                                                                          |                                                                                                                                                      |                                                                                         |                                                                                                                                          |  |  |  |  |  |

|------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|            |                                                  | Leub<br>Leub<br>Li van                                                                                                                          | *                                                                        | ••••••<br>•••••                                                                                                                                      | <u>(anna 9</u>                                                                          | -0-0-                                                                                                                                    |  |  |  |  |  |

| DEVICE     | RESONANT TUNNELING<br>DIODE - FET                | SINGLE<br>ELECTRON<br>TRANSISTOR                                                                                                                | RAPID SINGLE<br>QUANTUM FLUX<br>LOGIC                                    | QUANTUM<br>CELLULAR<br>AUTOMATA                                                                                                                      | NANOTUBE<br>DEVICES                                                                     | MOLECULAR DEVICES                                                                                                                        |  |  |  |  |  |

| TYPES      | 3-Terminal                                       | 3-Terminal                                                                                                                                      | Josephson<br>Junction<br>+Inductance<br>Loop                             | -Electronic QCA<br>-Magnetic QCA                                                                                                                     | FET                                                                                     | 2-Terminal and<br>3-Terminal                                                                                                             |  |  |  |  |  |

| ADVANTAGES | Density,<br>Performance,<br>RF                   | Density,<br>Power,<br>Function                                                                                                                  | High Speed,<br>Potentially<br>Robust,<br>(Insenstive to<br>Timing Error) | High Functional<br>Density,<br>No Interconnect<br>in Signal Path,<br>Fast and Low<br>Power                                                           | Density,<br>Power                                                                       | Identity of<br>Individual<br>Switches (e.g.,<br>Size, Properties<br>on Sub-nm Level.<br>Potential Solution<br>to Interconnect<br>Problem |  |  |  |  |  |

| CHALLENGES | Matching of Device<br>Properties Across<br>Wafer | New Device<br>and System,<br>Dimensional<br>Control (e.g.,<br>Room Temp<br>Operation),<br>Noise (Offset<br>Charge),<br>Lack of Drive<br>Current | Low<br>Temperatures,<br>Fabrication of<br>Complex, Dense<br>Circuity     | Limited Fan Out,<br>Dimensional<br>Control (Room<br>Temperature<br>Operation),<br>Architecture,<br>Feedback from<br>Devices,<br>Background<br>Charge | New Device and<br>System,<br>Difficult Route<br>for Fabricating<br>Complex<br>Circuitry | Thermal and<br>Environmental<br>Stability,<br>Two Terminal<br>Devices,<br>Need for New<br>Architectures                                  |  |  |  |  |  |

| MATURITY   | Demonstrated                                     | Demonstrated                                                                                                                                    | Demonstrated                                                             | Demonstrated                                                                                                                                         | Demonstrated                                                                            | Demonstrated                                                                                                                             |  |  |  |  |  |