Classification according to internal structure and operation/function:

- storage register;

- shift register

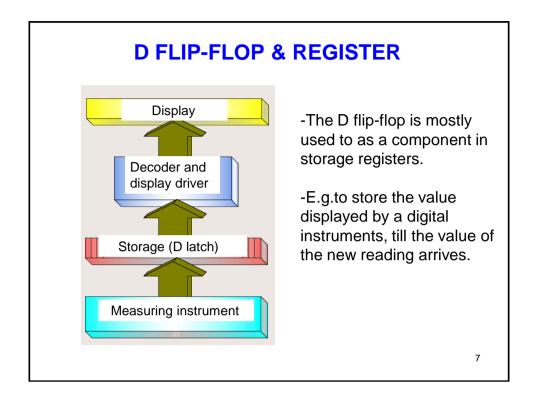

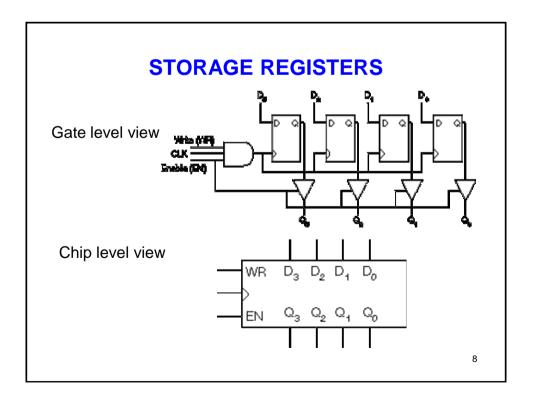

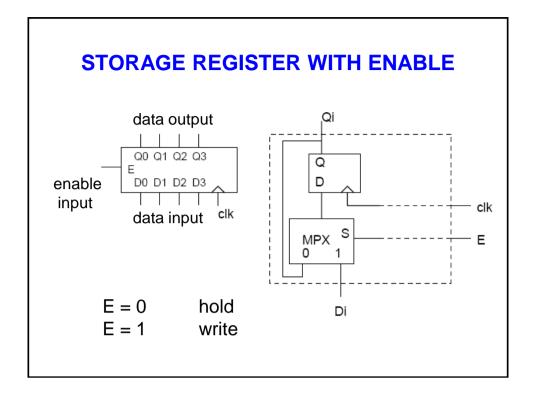

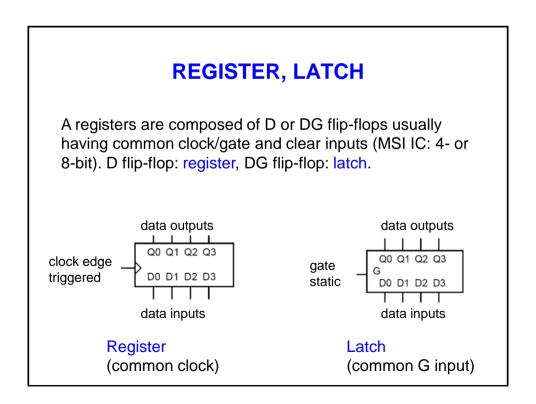

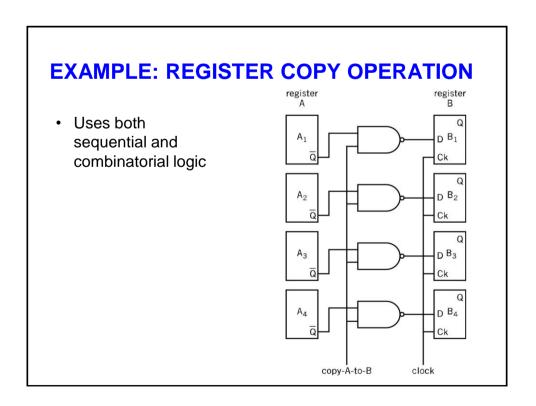

Storage register: it takes data from parallel inputs and copies it to the corresponding output when the registers are clocked. It can be used as a kind of "history", retaining old information as the input in another part of the system, until ready for new information, whereupon, the registers are clocked, and the new data is "let through". It is usually built using D flip-flops.

# USES OF STORAGE REGISTERS arithmetical units; temporary storage between counter and display; code and signal conversion operations; input/output storage registers in μPs; intermediate storage functions in arithmetic/logic units (ALU); various types of other temporary storage functions.

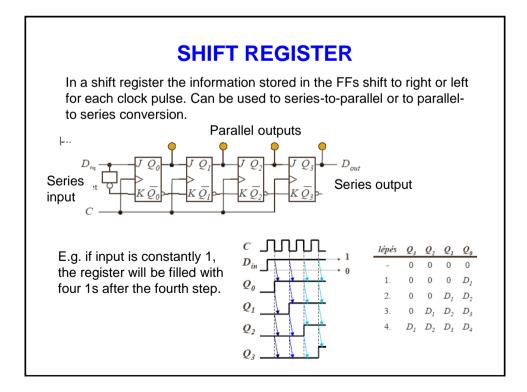

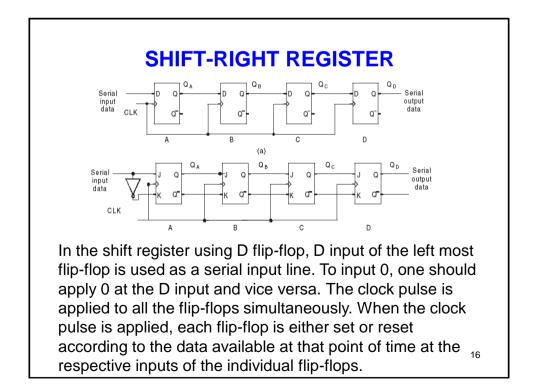

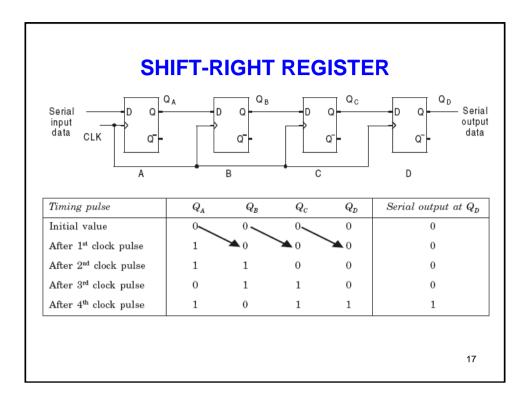

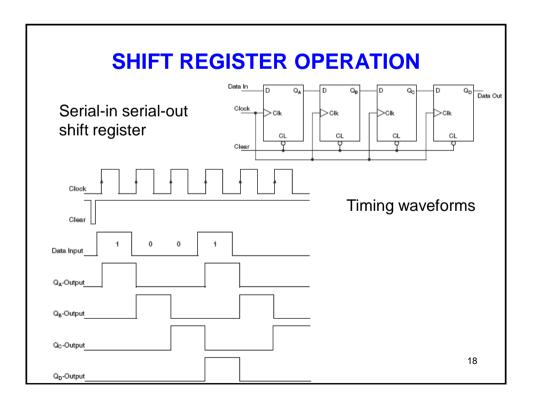

### SHIFT REGISTERS

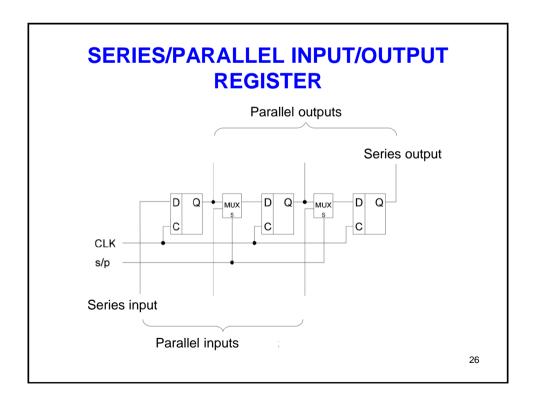

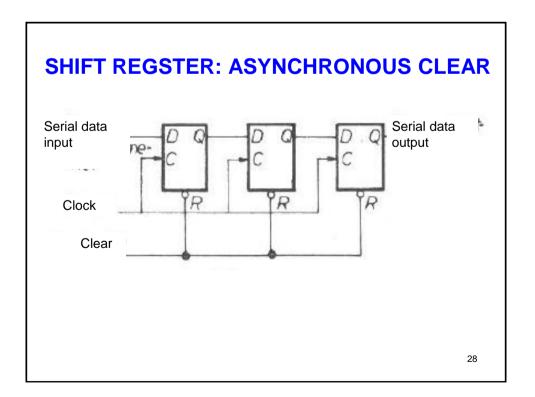

- The shift function of a register allows the stored data to be moved serially from stage to stage or into or out if the register.

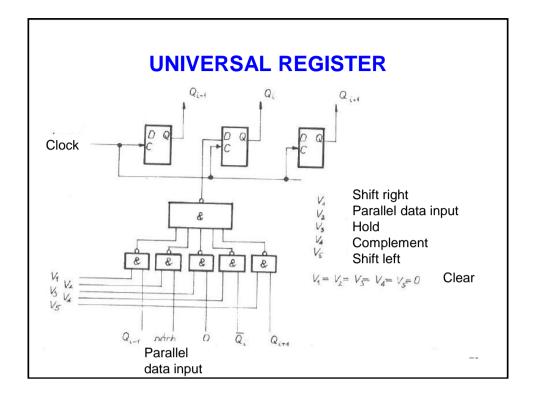

- Types of data movement:

- serial shift right or left

- parallel shift in to and out

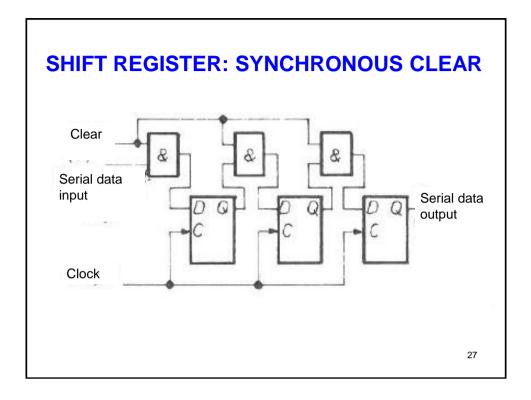

- The shift is executed by the synchronizing or clock signal.

- Register are used for conversion of data form serial to parallel and vice versa. Also used as counters.

- In shift registers the flip-flop types used should not be transparent. Usually master-slave types are used.

### SHIFT REGISTERS: CHARACTERISTIC EQUATIONS

Right shift register:

$Q_i^n = Q_{i+1}^{n-1}$

Left shift register:

$Q_{i}^{n} = Q_{i-1}^{n-1}$

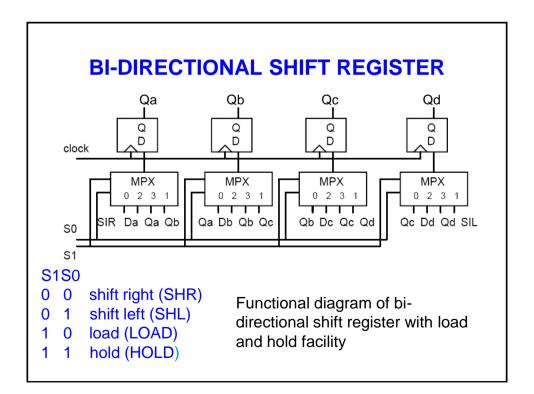

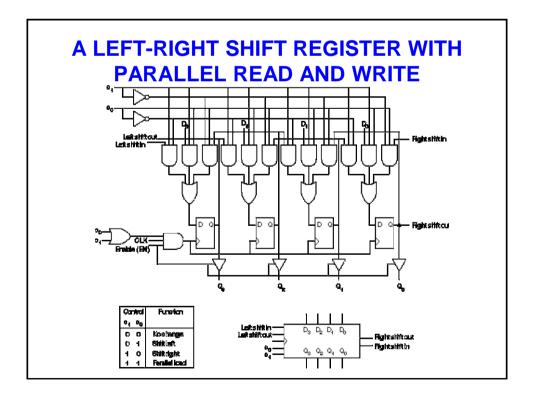

Bi-directional shift register Right sift (M=1) - left shift (M = 0):

$$Q_i^n = M Q_{i-1}^{n-1} + M Q_{i+1}^{n-1}$$

| SHIFT | REGIS | TER | TRU | ITH TABLE |    |

|-------|-------|-----|-----|-----------|----|

| CLK   | Q1    | Q2  | Q3  | Q4        |    |

| 1     | D1    | -   | -   | -         |    |

| 2     | D2    | D1  | -   |           |    |

| 3     | D3    | D2  | D1  | -         |    |

| 4     | D4    | D3  | D2  | D1        |    |

| 5     | D5    | D4  | D3  | D2        |    |

| 6     | D6    | D5  | D4  | D3        |    |

| 7     | D7    | D6  | D5  | D4        |    |

|       |       |     |     |           | 15 |

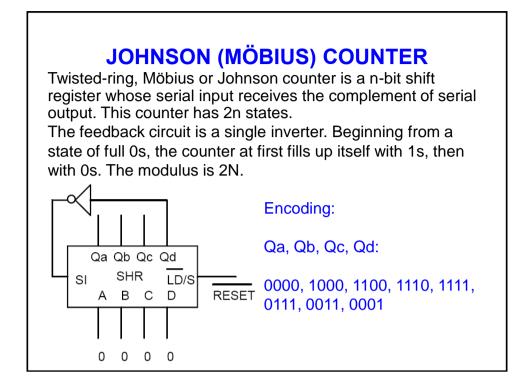

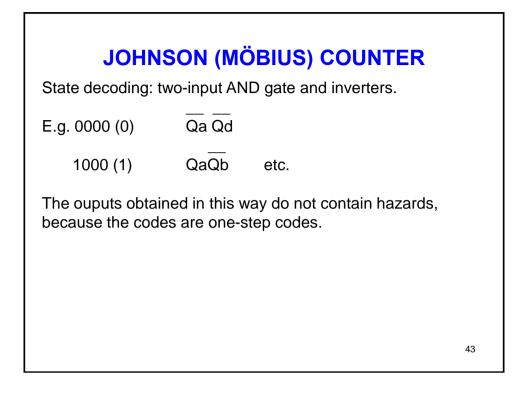

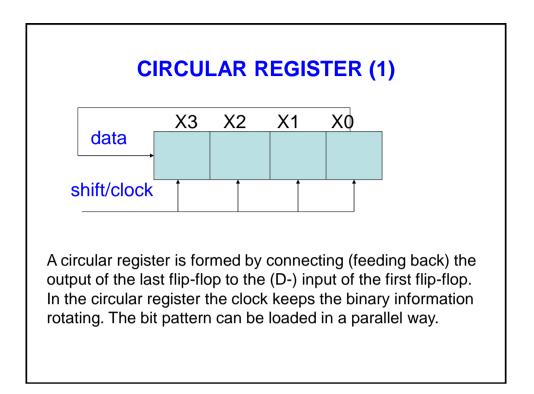

# SHIFT REGISTER COUNTERS

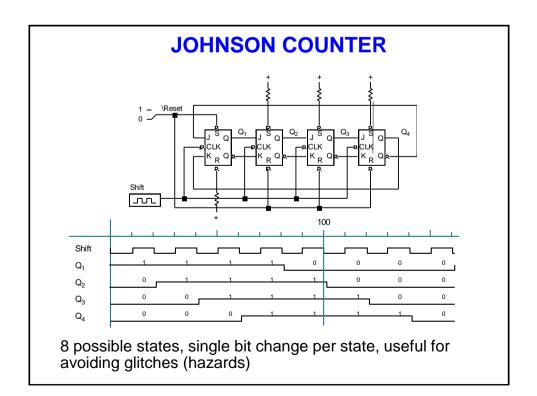

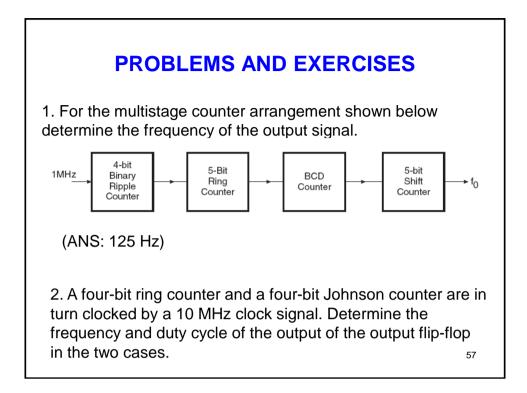

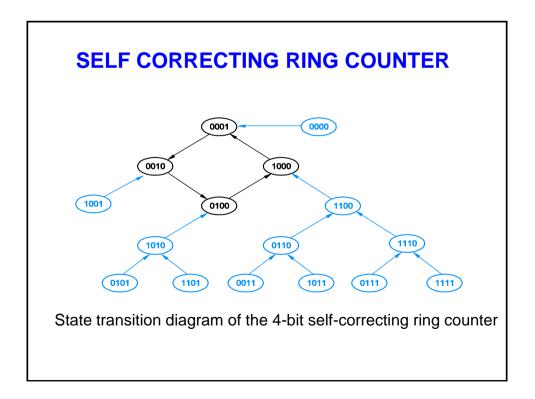

*Shift register counter* – a circuit formed by a shift registers and combinational logic. The state diagram for this state machine is cyclic. This circuit does not necessarily count in ascending or descending order.

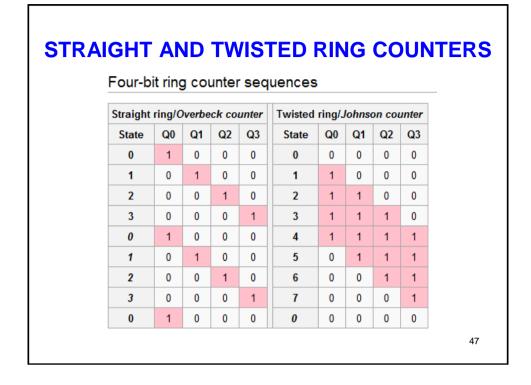

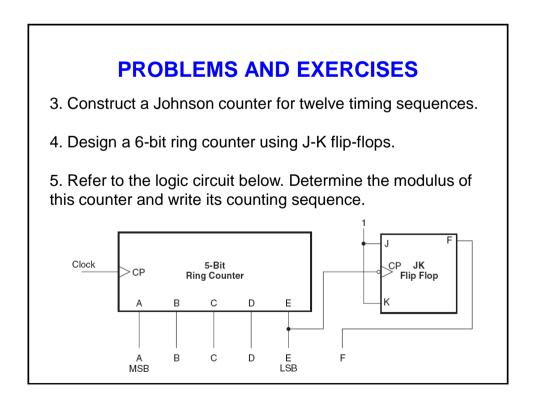

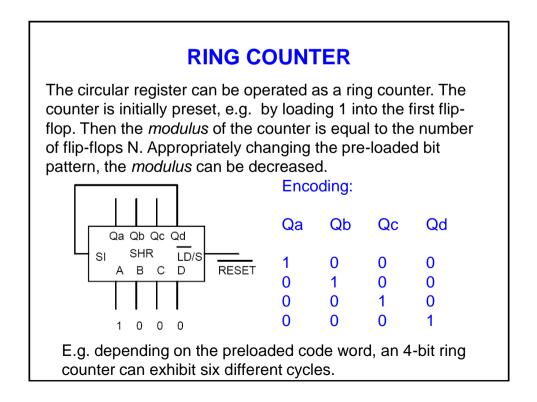

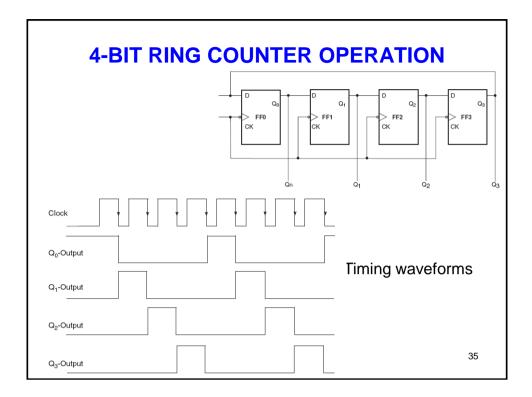

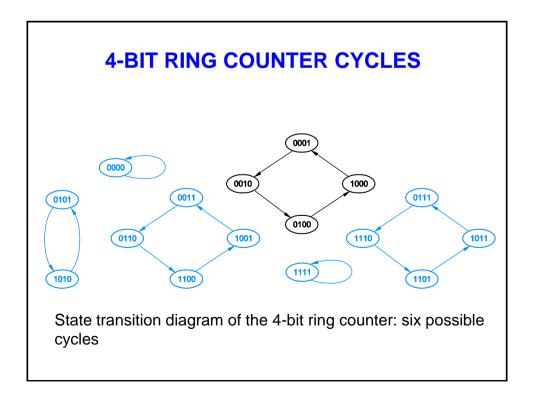

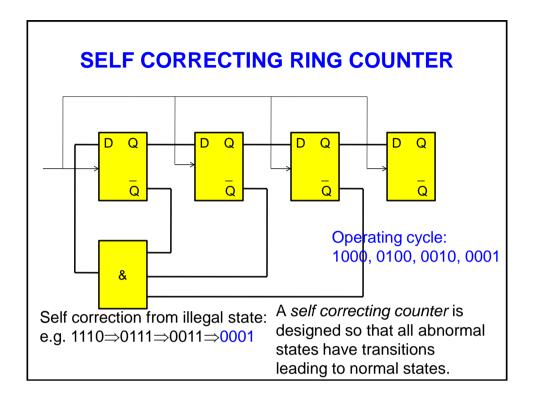

*Ring counter* – the simplest shift register counter. This circuit uses a *n*-bit shift register to obtain a counter with *n* states

39

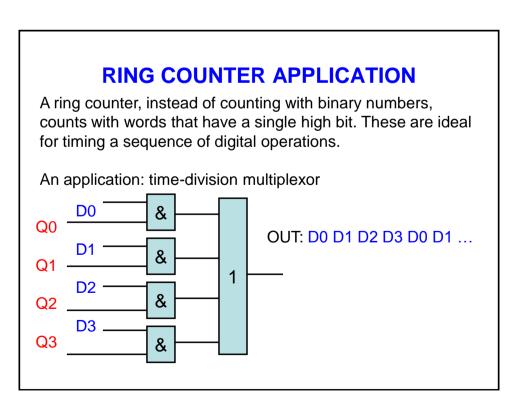

## **RING COUNTER APPLICATIONS**

Signal series generated by ring counter state can be used for control purposes.

Similar signal series can also be generated by a counterdecoder system, however in such case greater then one Hamming distance codes can be present on the decoder input. This can lead to the occurrence of functional hazards.