1

# **DIGITAL TECHNICS II**

### Dr. Bálint Pődör

Óbuda University, Microelectronics and Technology Institute

## 8. LECTURE: LOGIC CIRCUITS III: ECL, SCHOTTKY TTL, CMOS AND BICMOS

2nd (Spring) term 2017/2018

# 8. LECTURE

- 1. Digital IC technology picture gallery

- 2. Emitter coupled logic (ECL)

- 3. "Classical" and high performance ("advanced") logic families, performance comparisons

- 4. Advanced Schottky TTL logic families

- 5. Advanced CMOS circuits and logic families

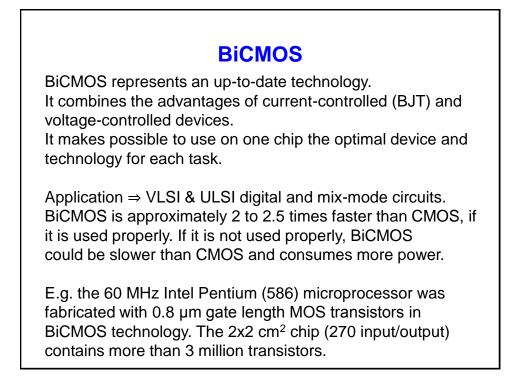

- 6. BiCMOS logic families

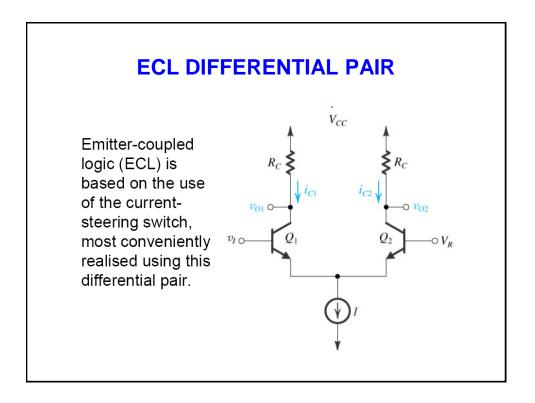

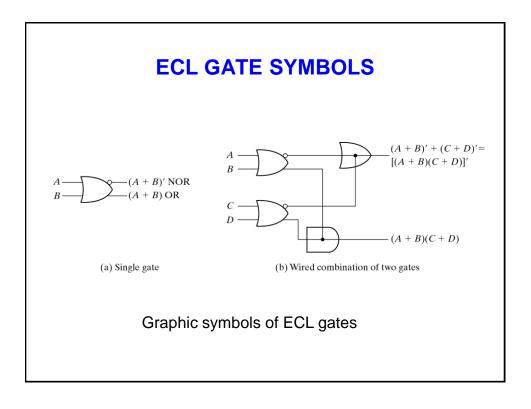

# EMITTER COUPLED LOGIC (ECL)

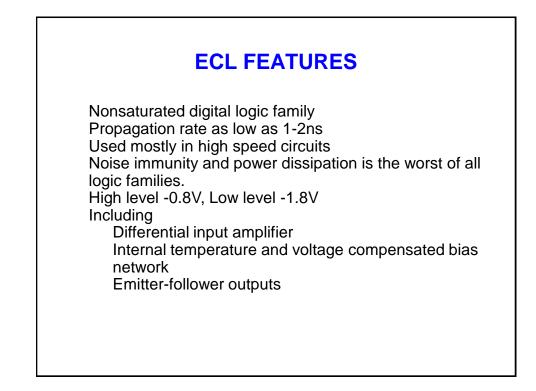

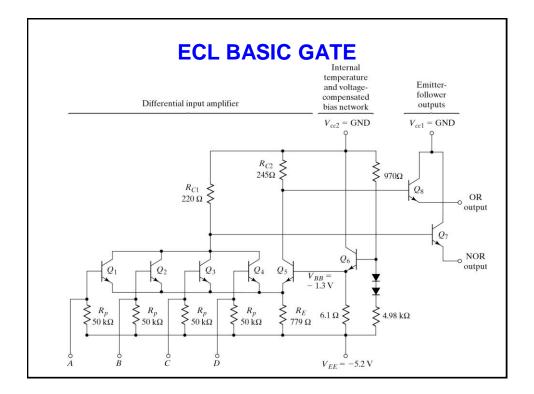

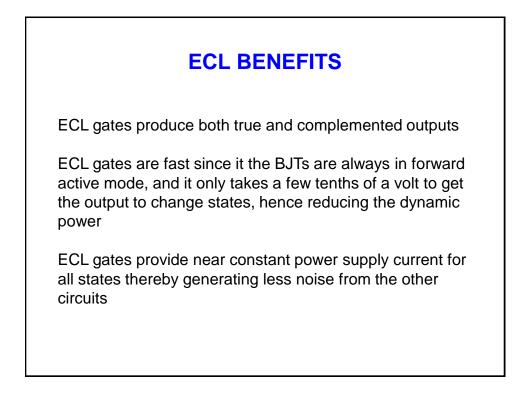

The ECL family (also called current-mode logic, CML) is the fastest logic family in the group of bipolar logic families. The characteristic features that give this logic family its high speed or short propagation delay are outlined as follows:

1. It is a nonsaturating logic. That is, the transistors in this logic are always operated in the active region of their output characteristics. They are never driven to either cutoff or saturation, which means that logic LOW and HIGH states correspond to different states of conduction of various bipolar transistors. The main factor, limiting the switching speed of TTL type circuits, the minority carrier storage is not present or at least is very weak.

# **EMITTER COUPLED LOGIC (ECL)**

2. The logic swing, that is, the difference in the voltage levels corresponding to logic LOW and HIGH states, is kept small (typically 0.85 V), with the result that the output capacitance needs to be charged and discharged by a relatively much smaller voltage differential.

3. The circuit currents are relatively high and the output impedance is low, with the result that the output capacitance can be charged and discharged quickly.

# **COMPARISON OF LOGIC FAMILIES**

| Parameter            | CMOS      | TTL       | ECL    |

|----------------------|-----------|-----------|--------|

| Basic gate           | NAND/NOR  | NAND      | OR/NOR |

| Fan-out              | >50       | 10        | 25     |

| Power per gate (mW)  | 1 @ 1 MHz | 1 - 22    | 4 - 55 |

| Noise immunity       | Excellent | Very good | Good   |

| t <sub>PD</sub> (ns) | 1 - 200   | 1.5 – 33  | 1 - 4  |

# <section-header> **TRANSISTOR-TRANSISTOR LOGIC TTL**The original basic TTL gate was a slight improvement over the DTL gate. There are several TTL subfamilies or series of the TTL technology. Thas a number start with 74 and follows with a suffix that identifies the series type, e.g. 7404, 74S86, 74ALS161. Three different types of output configurations: . open-collector output . Three-state (or tristate) output 74 – standard 54 – military 84 – industrial (discontinued)

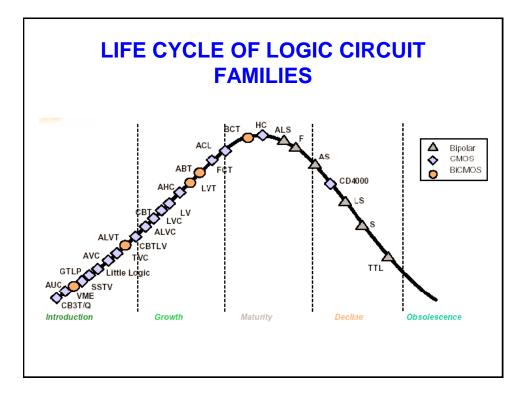

# HIGH SPEED/HIGH PERFORMANCE LOGIC COMPONENTS

Components for today's high-speed systems:

- Advanced Schottky transistor-transistor logic (TTL)

- Advanced complementary metal-oxide semiconductor (CMOS)

- Bipolar combined with CMOS (BiCMOS)

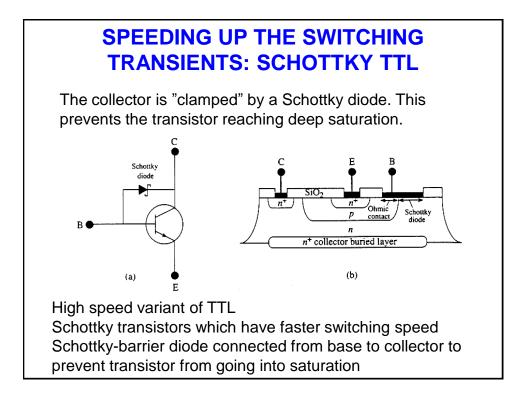

# **SCHOTTKY TTL: AN INTRODUCTION**

Transistor in bipolar logic (standard TTL) are saturated switches - minority carrier storage limits the speed of the device.

Variations of the standard TTL design to reduce these effects and improve speed, power consumption, or both.

"Schottky transistors" i.e. junction transistors with integrated Schottky barrier clamping diodes between the collector and basis reduce or prevent charge storage, leading to faster switching gates.

Incorporating Schottky barrier diodes into the TTL design, the switching speed can be reduced to 2 ... 5 nsec, a half or full order of magnitude improvement with respect to conventional design.

# **SCHOTTKY DIODE I-V CHARACTERISTICS**

- Schottky diode is a metal-semiconductor (MS) diode

- Historically, Schottky diodes are the oldest diodes

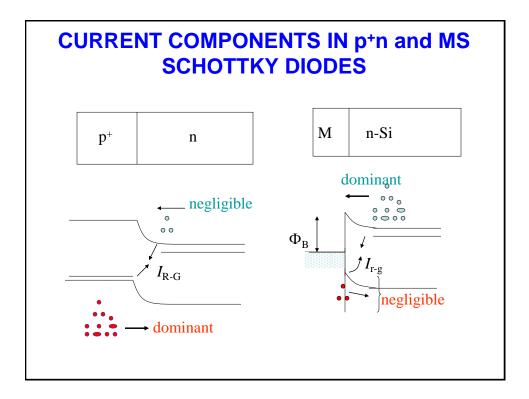

- MS diode electrostatics and the general shape of the MS diode I-V characteristics are similar to p<sup>+</sup>n diodes, but the details of current flow are different.

- Dominant currents in a p+n diode

- arise from recombination in the depletion layer under small forward bias.

- arise from hole injection from p<sup>+</sup> side under larger forward bias.

- · Dominant currents in a MS Schottky diodes

- Electron injection from the semiconductor to the metal.

# **I-V CHARACTERISTICS**

$$I = I_{s} \left( e^{\frac{qV_{A}}{kT}} - 1 \right) \text{ where } I_{s} = A \mathcal{A}^{*} T^{2} e^{-\frac{\Phi_{B}}{kT}}$$

where  $\Phi_{\rm B}$  is Schottky barrier height,  $V_{\rm A}$  is applied voltage, A is area, and  $A^*$  is Richardson's constant.

The reverse leakage current for a Schottky diode is generally much larger than that for a p<sup>+</sup>n diode.

Since MS Schottky diode is a majority carrier devices, the frequency response of the device is much higher than that of equivalent  $p^+$  n diode.

### Features:

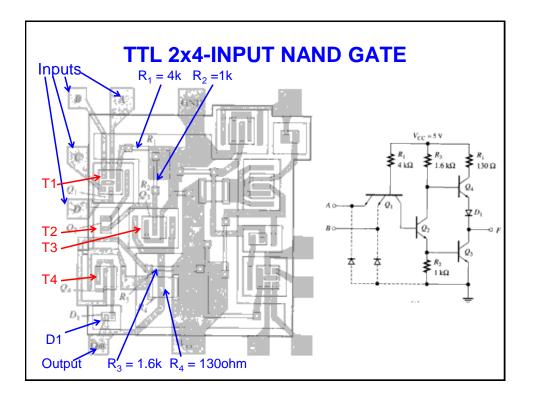

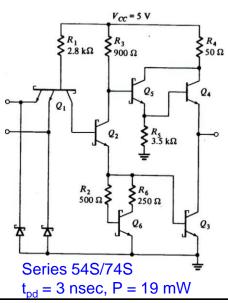

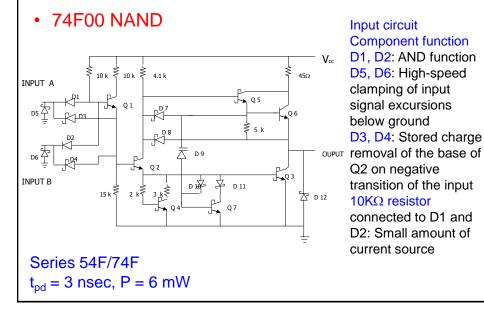

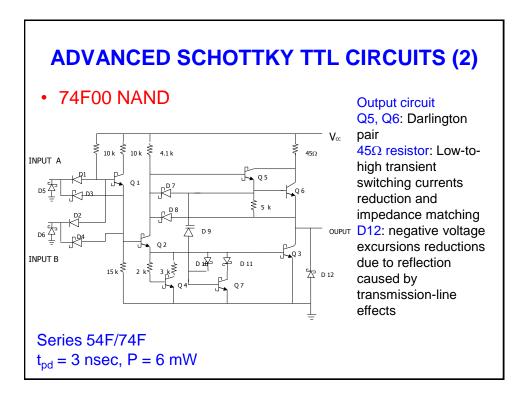

Transistors: all clamped with Schottky diode except Q4 (this does not saturate) Input diodes: high-speed clamping of input signal excursions below ground Q5: Emitter follower to speed up 0-to-1 switching of output 50 ohm resistor: Low-to-high transient switching current reduction and impedance matching

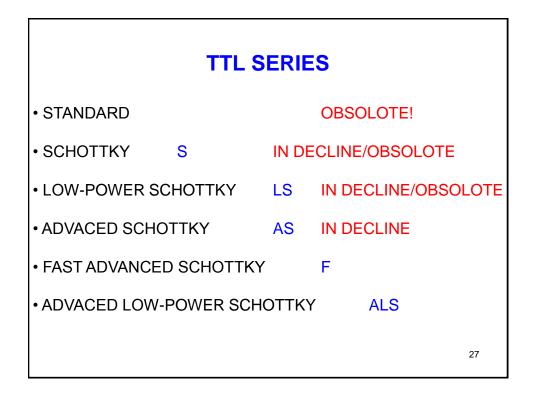

# ADVANCED SCHOTTKY TTL LOGIC FAMILIES

- Letter designator

- F: fast advanced Schottky TTL

- ALS: advanced low-power Schottky TTL

- AS: advanced Schottky TTL

- Selection criteria of FAST vs. AS

- Price, availability

# **ADVANCED SCHOTTKY TTL CIRCUITS (1)**

# CMOS AND ADVANCED CMOS: SURVEY

С - 4-15 V operation (similar to 4000 series) - High speed, similar performance to LS HC HCT - high speed, compatible logic levels to bipolar parts - Advanced, performance generally between S and F AC AHC - Advanced high speed, 3x faster than HC FC - Fast, performance similar to F LCX - 3V supply and 5 volt tolerant inputs LVQ - Low voltage 3.3 V LVX - Low voltage 3.3 V with 5 V tolerant inputs VHC - very high speed "S" performance in CMOS G - super high speed, more than 1 GHz Many parts of the HC, AC, and FC families are available in "T" versions, i.e. with input thresholds compatible with both TTL and 3.3 V CMOS signals.

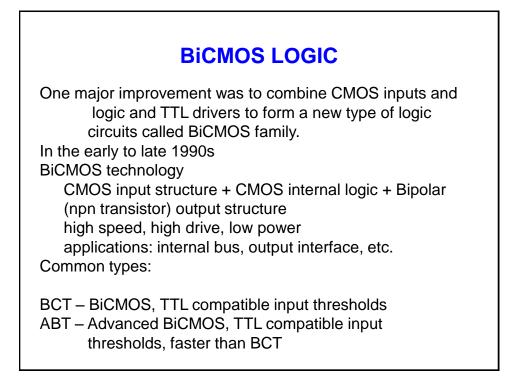

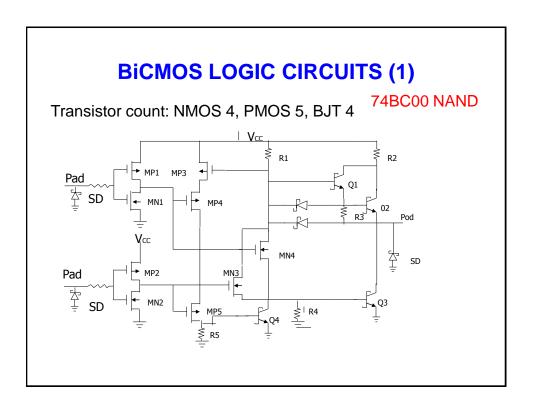

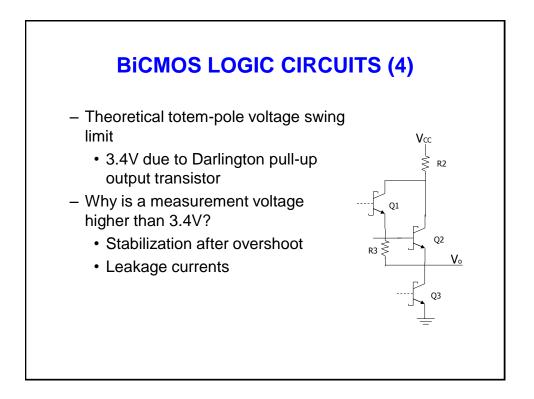

# **BiCMOS LOGIC CIRCUITS (2)**

- Bipolar totem-pole output stage

- Advantage

- By totem-pole stage output voltage swing

- Less dynamic power

- Less crosstalk

- Less transient switching current

- » Less ground bounce, less power and reference level corruption

# **BiCMOS LOGIC CIRCUITS (3)**

- By resistor R2

- Reduction of low-to-high transient switching current

- Low-to-high output impedance matching to PCB trace

- More stable with temperature than MOSFETs

- In CMOS, when 1°C increases

- » 6% impedance change

- » 3% speed change (slow down)

# **BICMOS: APPLICATION EXAMPLES**

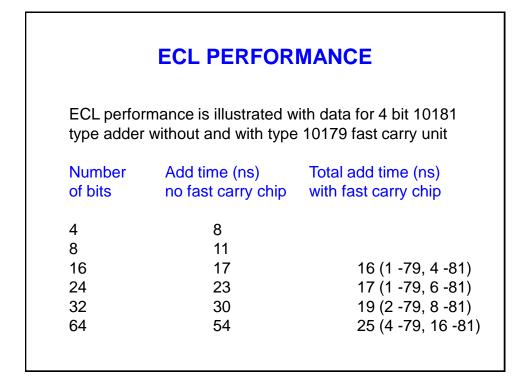

Carry look ahead in adders: the carry can be calculated from the *generate* and *propagate* combinations. Fast operation is ensured by using bipolar output stages in the implementation of

$$C_{i+1} = G_i + P_i C_i$$

allowing a fast charging of the loading capacitances.

Other example is the driving of buses, which also represent relatively large capacitive loads.

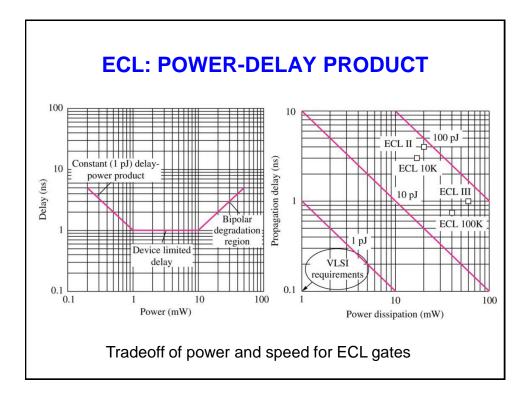

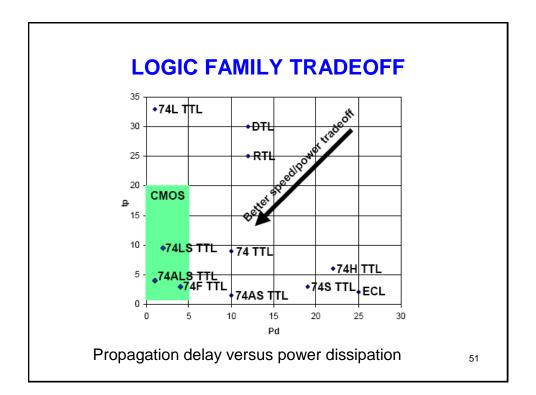

# FIGURE-OF-MERIT: POWER-DELAY PRODUCT

The product of the average power consumption and average propagation delay. Since the clock cycle is limited by the propagation delay, this number is essentially the typical energy consumption per cycle per gate.

Values are currently in the picoJoule range.

On thing that makes this a good *figure-of-merit* is that many of the simple things one can do to improve (decrease) propagation delay essentially increases (degrades) the current and thus the power consumption, so the PDP remains constant.

# **POWER-DELAY PRODUCT**

"Good" circuit: small delay and small power dissipation.

Figure-of-merit: the product of these two parameters (power-delay product).

Standard 54/74 series:  $t_{od}$  = 10 nsec, P = 10 mW/gate

$$P t_{pd} = 100 pJ$$

Interpretation: approximately the energy needed to change the value of 1 bit.

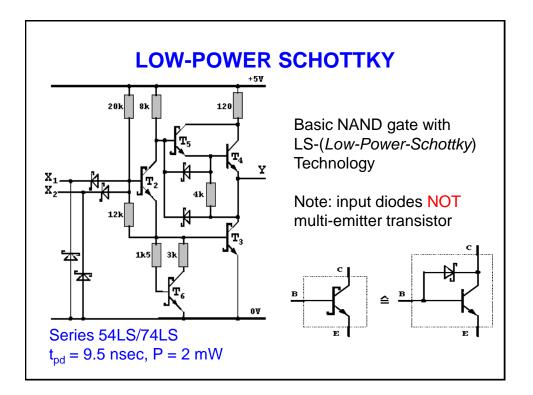

# SCHOTTKY TTL: POWER-DELAY PRODUCT

54S/74S series:  $t_{pd}$  = 3 nsec, P = 19 mW/gate

$P t_{pd} = 57 pJ$

54LS/74LS series:  $t_{pd}$  = 9 nsec, P = 2 mW/gate

$P t_{pd} = 18 pJ$

A factor of 1.5 and 5 better than standard TTL!

# TTL AND CMOS: $P_{\tau}$ FIGURE OF MERIT

| Circuit<br>family | Propagation delay    | Gate<br>dissipation | "Jósági"<br>tényező |

|-------------------|----------------------|---------------------|---------------------|

| lanny             | t <sub>pd</sub> [ns] | $P_{d}$ [mW]        | Pd*tpd [pJ]         |

| 74xx              | 10                   | 10                  | 100                 |

| 74LSxx            | 9.5                  | 2                   | 19                  |

| 74ASxx            | 1.5                  | 2                   | 13                  |

| 74ALSxx           | 4                    | 1.2                 | 5                   |

| 74Fxx             | 3                    | 6                   | 18                  |

| 74HCxx            | 8                    | 0.003               | $24 \times 10^{-3}$ |

| 74HCTxx           | 14                   | 0.003               | $42 \times 10^{-3}$ |

| 74ACxx            | 5                    | 0.010               | $50 \times 10^{-3}$ |

| 74ACTxx           | 5                    | 0.010               | $50 \times 10^{-3}$ |

| 74AHCxx           | 5.5                  | 0.003               | $16 \times 10^{-3}$ |

| 74AHCTxx          | 5                    | 0.003               | $14 \times 10^{-3}$ |

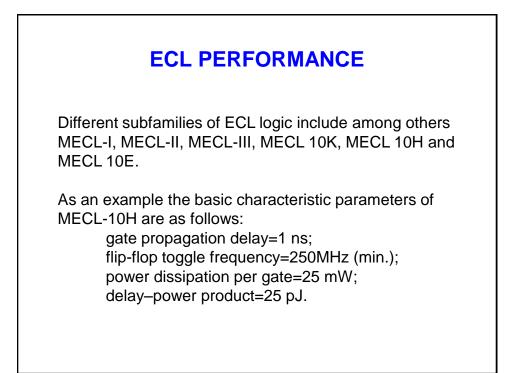

| 10xxx             | 2                    | 25                  | 50                  |

| 10Hxxx            | 1                    | 25                  | 25                  |

# FET (MOSFET) PHYSICAL SPEED LIMIT

Absolute upper limit for all transit-time type devices: transit time or transit frequency

$f_{max} \leq f_t = 1 / (2 \pi \tau_t)$  (unity gain!)

Si 0.8 µm MOS transistor (Intel Pentium, 60 MHz):

$v_{sat} = 5x10^{6}$  cm/sec (electrons) (Si material parameter)  $L_{gate} = 0.8 \ \mu m$  $T_t = L_{gate} / v_{sat} = 16 \ psec$

$f_{max} \le 10 \text{ GHz}$  (unity gain)

Clock frequency is much less of course! E.g.  $f_{3dB} > f_{clock}$ To avoid distorsion minimum 3rd harmonic is necessary!

# BIPOLAR AND MOS COMPARISON

| Property           | Bipolar             | MOS              |

|--------------------|---------------------|------------------|

| Power dissipation  | medium              | very small       |

| Switching time     | very small          | relatively small |

| Input impedance    | small               | extremely large  |

| Loading capability | good                | very good        |

| Noise              | small               | very small       |

| Fab technology     | more complex        | more simple      |

| Integration        | less (in principle) | very high        |

# **REVISION QUESTIONS**

1. Why is ECL called nonsaturating logic? What is the main advantage accruing from this? With the help of a relevant circuit schematic, briefly describe the operation of ECL OR/NOR logic.

2. What are the Schottky diode and Schottky transistor?

3. What is Bi-CMOS logic? What are its advantages?

4. Draw the basic BiCMOS inverter and explain.

5. Compare the characteristics of different logic families.

# **REVISION QUESTIONS**

6. Explain the concept of power-delay product as a figure of merit.

7. Compare the standard TTL, low-power Schottky TTL and Schottky TTL on the basis of speed and power dissipation.